## Noise Shaping Techniques for Analog and Time to Digital Converters Using Voltage Controlled Oscillators

by

Matthew A. Z. Straayer

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2008

© Matthew A. Z. Straayer, MMVIII. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

| Author.   |            |                               |                     |

|-----------|------------|-------------------------------|---------------------|

|           | Department | of Electrical Engineering and | l Computer Science  |

|           |            |                               | May 21, 2008        |

| Certified | by         |                               |                     |

|           |            |                               | Michael H. Perrott  |

|           |            |                               | Associate Professor |

|           |            |                               | Thesis Supervisor   |

| Accepted  | l by       |                               |                     |

|           | -          |                               | Terry P. Orlando    |

|           | Chairman   | Department Committee on       | Graduate Students   |

## Noise Shaping Techniques for Analog and Time to Digital Converters Using Voltage Controlled Oscillators

by

Matthew A. Z. Straayer

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2008, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

Advanced CMOS processes offer very fast switching speed and high transistor density that can be utilized to implement analog signal processing functions in interesting and unconventional ways, for example by leveraging time as a signal domain. In this context, voltage controlled ring oscillators are circuit elements that are not only very attractive due to their highly digital implementation which takes advantage of scaling, but also due to their ability to amplify or integrate conventional voltage signals into the time domain. In this work, we take advantage of voltage controlled oscillators to implement analog- and time-to-digital converters with first-order quantization and mismatch noise-shaping.

To implement a time-to-digital converter (TDC) with noise-shaping, we present a oscillator that is enabled during the measurement of an input, and then disabled in between measurements. By holding the state of the oscillator in between samples, the quantization error is saved and transferred to the following sample, which can be seen as first-order noise-shaping in the frequency domain. In order to achieve good noise-shaping performance, we also present key details of a multi-path oscillator topology that is able to reduce the effective delay per stage by a factor of 5 and accurately preserve the quantization error from measurement to measurement.

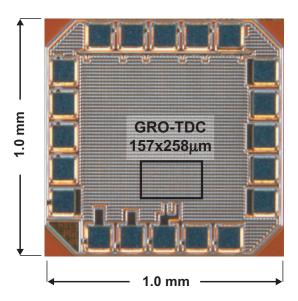

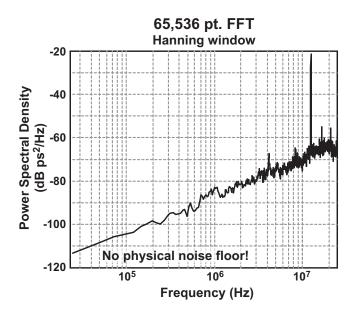

An 11-bit, 50Msps prototype time-to-digital converter (TDC) using a multi-path gated ring oscillator with 6ps of delay per stage demonstrates over 20dB of 1st-order noise shaping. At frequencies below 1MHz, the TDC error integrates to  $80 \mathrm{fs_{rms}}$  for a dynamic range of 95dB with no calibration of differential non-linearity required. The  $157\mathrm{x}258\mu\mathrm{m}$  TDC is realized in  $0.13\mu\mathrm{m}$  CMOS and operates from a  $1.5\mathrm{V}$  supply.

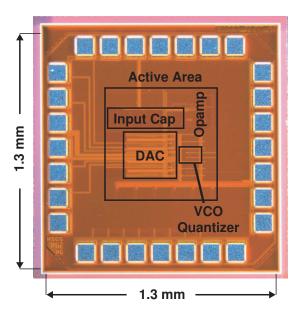

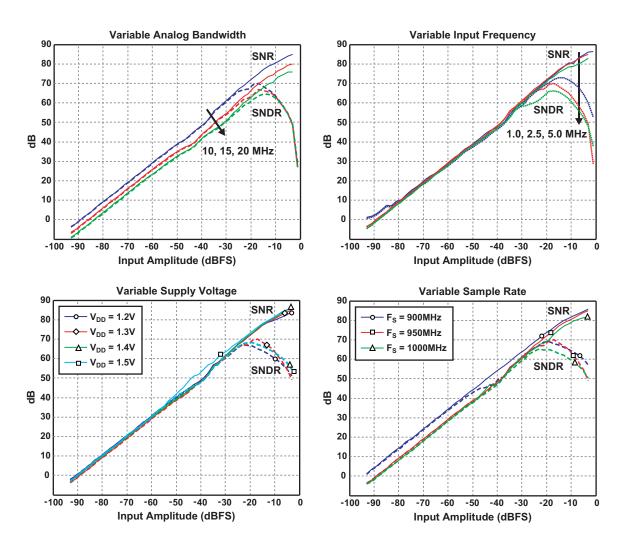

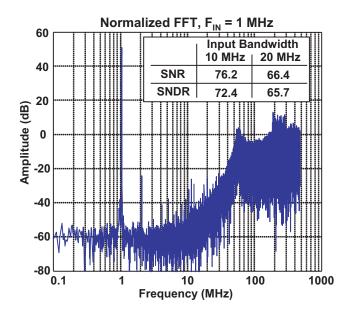

The use of VCO-based quantization within continuous-time (CT)  $\Sigma\Delta$  ADC structures is also explored, with a custom prototype in  $0.13\mu\mathrm{m}$  CMOS showing measured performance of 86/72dB SNR/SNDR with 10MHz bandwidth while consuming 40mW from a 1.2V supply and occupying an active area of  $640\mu\mathrm{m}$  X  $660\mu\mathrm{m}$ . A key element of the ADC structure is a 5-bit VCO-based quantizer clocked at 950 MHz which we show achieves first-order noise-shaping of its quantization noise. The quantizer structure allows the second order CT  $\Sigma\Delta$  ADC topology to achieve third order noise

shaping, and direct connection of the VCO-based quantizer to the internal DACs of the ADC provides intrinsic dynamic element matching (DEM) of the DAC elements.

Thesis Supervisor: Michael H. Perrott

Title: Associate Professor

#### Acknowledgments

I owe much to Michael Perrott, who has freely given his time to me and this work, and who has pushed me to think hard about fundamentals, and to balance my instinct with reason. Collaborating with him on this work has simply been a pleasure. Hae-Sung Lee has helped guide this work in numerous ways with constant support, quite literally from the very first day. My colleagues at MIT have provided wonderful feedback, ideas, and friendship. I thank Belal Helal for his diligence in testing TDC deadzones, and for first demonstrating the GRO-TDC in a system. Chun-Ming Hsu provided many ideas for the GRO, and his excellent work on the digital PLL proved to be a wonderful demonstration of the GRO-TDC at the system level. Matt Park and Min Park provided invaluable feedback on the ADC, and Charlotte Lau and Kerwin Johnson helped immeasurably with administering software.

The opportunity for me to work on this research was made possible by the generous support from MIT Lincoln Laboratory, and for that support I am truly grateful. Mark Gouker's leadership, vision, and mentorship throughout the process has been both encouraging and insightful. I am thankful to the Lincoln Scholars Program and to Dave Shaver for their committment to fund this work, and to Tim Hancock, who many times helpfully lent his ear as well as his constructive feedback. I thank Andy Messier for his willingness to debug verilog code with me, George Fitch for providing GPIB code, and also Rick Slattery, Peter Murphy, and Lenny Johnson for support with packaging.

Thanks are in order to Frequency Electronics, Inc. for providing access to high-quality quartz oscillators for testing the fractional / integer digital PLL. In addition, many people in the high-speed data converters group at Analog Devices, Inc. provided helpful guidance and resources for testing the  $\Sigma\Delta$  ADC.

My wife, Mariah, has worked in so many ways to support my endeavors represented here, and I cannot overstate my gratitude of her faithfulness to me and our family. My children have kept me focused on the important priorities; they remind me each day of small joys that would otherwise go unnoticed. Abigail has shown me the joy of learning, Caleb the joy of exploration, Eliza the joy of accomplishment, and Levi, the joy of a good night's sleep. I am also deeply grateful to my parents, who have given me the foundation and freedom to undertake many adventures.

There are many others to thank as well, too many to list here. So to my extended family and friends who have supported me financially, spritually, and emotionally, I want to sincerely say thank you.

# Contents

| 1                                               | Intr | oducti  | ion                                       | 19 |

|-------------------------------------------------|------|---------|-------------------------------------------|----|

|                                                 | 1.1  | Area    | of focus                                  | 19 |

|                                                 | 1.2  | Prima   | ry contributions                          | 22 |

|                                                 | 1.3  | Thesis  | s overview                                | 24 |

| <b>2</b>                                        | Bac  | kgroui  | nd on Time-to-Digital Converters          | 25 |

|                                                 | 2.1  | Introd  | luction                                   | 25 |

|                                                 | 2.2  | TDC     | with gate-delay resolution                | 30 |

|                                                 | 2.3  | TDC     | with sub-gate-delay resolution            | 32 |

|                                                 | 2.4  | Oversa  | ampling TDC considerations                | 36 |

|                                                 | 2.5  | Oscilla | ator-based TDC                            | 39 |

|                                                 | 2.6  | Gated   | ring oscillator TDC                       | 42 |

| 3                                               | Det  | ailed ( | GRO operation                             | 47 |

| 3.1 Simple Gated Ring Oscillator Implementation |      |         | e Gated Ring Oscillator Implementation    | 47 |

|                                                 |      | 3.1.1   | GRO with inverter delay stages            | 47 |

|                                                 |      | 3.1.2   | Model for skew due to oscillator gating   | 49 |

|                                                 |      | 3.1.3   | Gating skew analysis                      | 53 |

|                                                 |      | 3.1.4   | Deadzone effects                          | 60 |

|                                                 |      | 3.1.5   | Improving the gating sensitivity function | 61 |

|                                                 | 3.2  | Multi-  | Path Gated Ring Oscillator                | 62 |

|                                                 |      | 3.2.1   | Achieving sub-gate-delay raw resolution   | 63 |

|                                                 |      | 3.2.2   | Design of the Proposed Multi-Path GRO     | 69 |

|   |     | 3.2.3 Non-linearity of the Proposed Multi-Path GRO          | 73          |

|---|-----|-------------------------------------------------------------|-------------|

| 4 | GR  | O readout techniques                                        | 81          |

|   | 4.1 | Measurement entirely with counters                          | 81          |

|   | 4.2 | A more efficient measurement technique                      | 83          |

|   |     | 4.2.1 Measuring frequency by tracking phase                 | 84          |

|   |     | 4.2.2 Robust de-glitch technique                            | 86          |

|   | 4.3 | Multi-path GRO-TDC implementation details                   | 91          |

|   |     | 4.3.1 Phase measurement of a 47-stage multi-path oscillator | 91          |

|   |     | 4.3.2 Other design considerations                           | 96          |

| 5 | GR  | O-TDC results and discussion                                | 99          |

|   | 5.1 | Measurement setup                                           | 100         |

|   | 5.2 | Inverter-based GRO-TDC measurements                         | 101         |

|   | 5.3 | Multi-path GRO-TDC measurements                             | 104         |

|   |     | 5.3.1 Delay, power, and efficiency performance              | 104         |

|   |     | 5.3.2 Noise shaping performance                             | 106         |

|   | 5.4 | Discussion                                                  | 109         |

| 6 | GR  | O-TDC applications and discussion                           | 113         |

|   | 6.1 | Digital PLL for wireless communication                      | 113         |

|   | 6.2 | PLL for timing synchronization                              | 119         |

|   | 6.3 | Very high-resolution frequency measurement                  | 124         |

| 7 | Bac | ekground on VCO-based quantizers                            | <b>12</b> 9 |

|   | 7.1 | Common VCO-quantizer implementations                        | 130         |

|   | 7.2 | SNDR limitations for VCO-based quantization                 | 135         |

|   |     | 7.2.1 Linear modeling                                       | 135         |

|   |     | 7.2.2 Theoretical SNR                                       | 138         |

|   | 7.3 | Example                                                     | 139         |

| 8  | VC             | O-base | ed quantizer $\Sigma\Delta$ ADC Architecture               | 143 |

|----|----------------|--------|------------------------------------------------------------|-----|

|    | 8.1            | Comp   | arison of VCO-based quantizer and comparator-based FLASH   |     |

|    |                | quanti | izer for $\Sigma\Delta$ ADC                                | 144 |

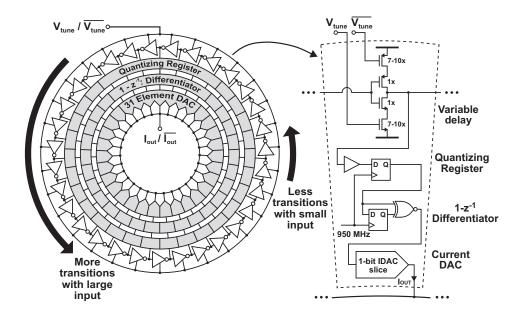

|    |                | 8.1.1  | Implicit Barrel-Shift DEM using the VCO-based quantizer $$ | 144 |

|    |                | 8.1.2  | Metastability                                              | 146 |

|    |                | 8.1.3  | Comparator Offset and Monotonicity                         | 148 |

|    |                | 8.1.4  | Power Supply Considerations                                | 149 |

|    | 8.2            | Model  | ling the suppression of VCO-based quantizer non-linearity  | 149 |

|    | 8.3            | Exam   | ple                                                        | 152 |

|    | 8.4            | Concl  | usion                                                      | 155 |

| 9  | Pro            | totype | e $\Sigma\Delta$ ADC with a VCO-quantizer                  | 157 |

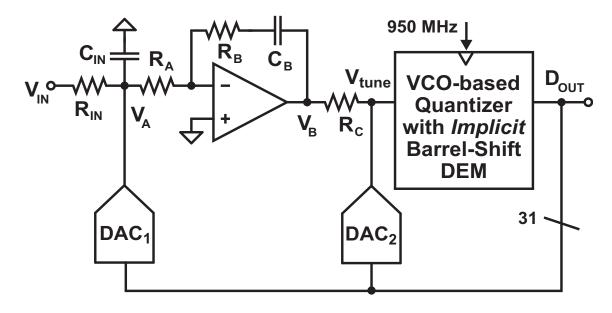

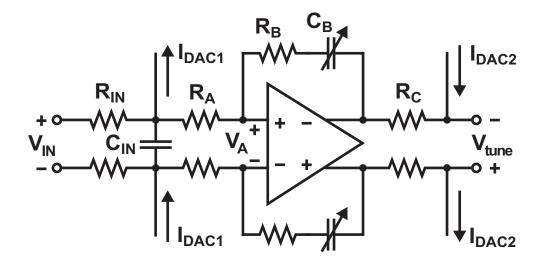

|    | 9.1            | ΣΔ Α   | DC Architecture                                            | 157 |

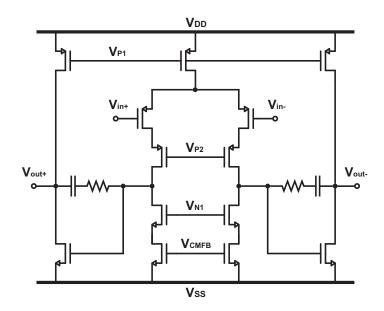

|    | 9.2            | Circui | t Implementation                                           | 159 |

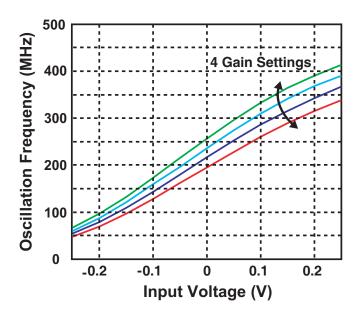

|    |                | 9.2.1  | VCO-based quantizer                                        | 159 |

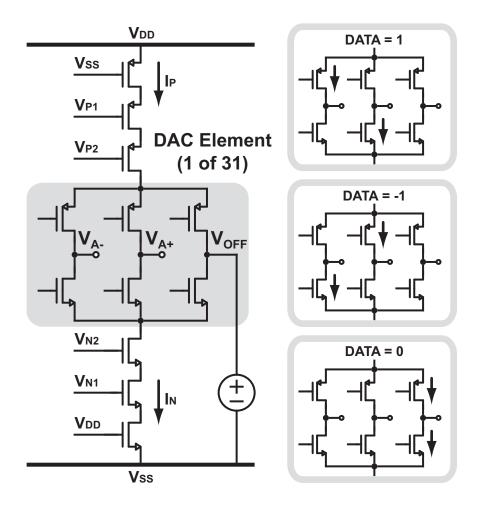

|    |                | 9.2.2  | DAC                                                        | 162 |

|    |                | 9.2.3  | Loop filter                                                | 164 |

| 10 | $\Sigma\Delta$ | ADC    | results and discussion                                     | 167 |

|    | 10.1           | Measu  | rement setup                                               | 167 |

|    | 10.2           | Measu  | rement results                                             | 169 |

|    | 10.3           | Discus | ssion                                                      | 171 |

| 11 | Con            | clusio | n                                                          | 173 |

# List of Figures

| 1-1  | VCO voltage-to-frequency and voltage-to-phase relationships               | 20 |

|------|---------------------------------------------------------------------------|----|

| 1-2  | The basic concept of a VCO-based ADC and TDC in this work $\ \ .$         | 21 |

| 2-1  | Reference and signal pulses vs. time                                      | 26 |

| 2-2  | Trends of reported TDC resolution versus CMOS technology                  | 28 |

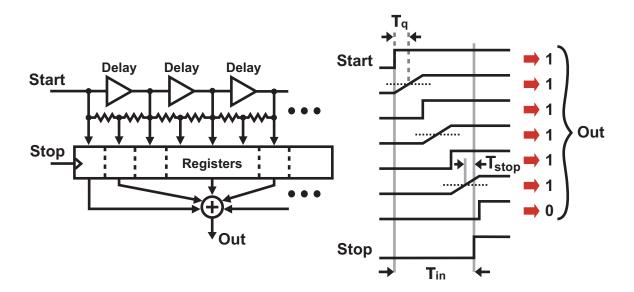

| 2-3  | Classical delay-chain TDC                                                 | 30 |

| 2-4  | A cyclic TDC based on re-using delay elements                             | 31 |

| 2-5  | An Vernier TDC that effectively amplifies the input time interval $$ . $$ | 33 |

| 2-6  | A dual-step TDC that incorporates both the delay-chain and Vernier        |    |

|      | techniques                                                                | 34 |

| 2-7  | An analog interpolating TDC that creates transitions with sub-gate-       |    |

|      | delay spacing                                                             | 35 |

| 2-8  | A digital technique for creating transitions with sub-gate-delay spacing  | 35 |

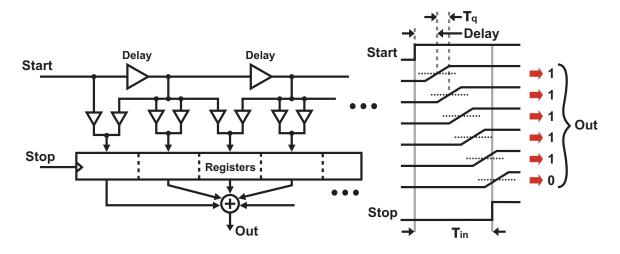

| 2-9  | Comparison of TDC DC transfer characteristics                             | 37 |

| 2-10 | Classical oscillator-based TDC                                            | 40 |

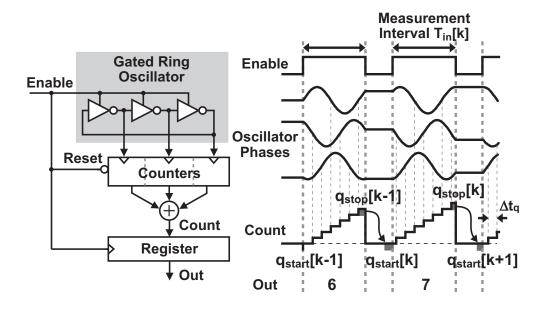

| 2-11 | Concept of the gated ring oscillator TDC                                  | 43 |

| 2-12 | Barrel-shifting of GRO delay elements to achieve first-order shaping of   |    |

|      | mismatch error                                                            | 44 |

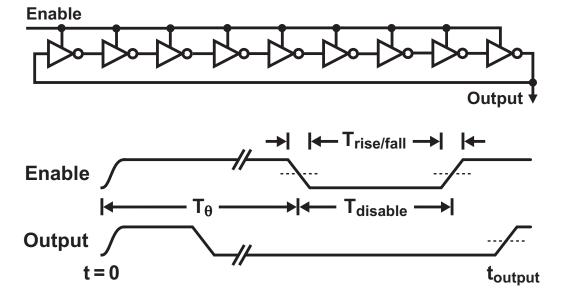

| 3-1  | Conceptual implementation of gating a ring oscillator                     | 48 |

| 3-2  | Transistor-level schematic of a simple GRO                                | 48 |

| 3-3  | Conceptual picture of a transition that is interrupted with a disable     |    |

|      | window                                                                    | 50 |

|      |                                                                           |    |

| 3-4  | Conceptual illustration of how charge redistribution within a delay                   |   |

|------|---------------------------------------------------------------------------------------|---|

|      | element depends on the input level                                                    | 5 |

| 3-5  | Phase trajectory skew (error) due to the physical non-idealities of gat-              |   |

|      | ing an oscillator                                                                     | 5 |

| 3-6  | Concept of how the gating skew error for an inverter-based GRO is the                 |   |

|      | sum of the skew from the positive and negative transitions                            | 5 |

| 3-7  | Simulation testbench to characterize $T_{skew}$ as a function of $\hat{\theta}_{GRO}$ | 5 |

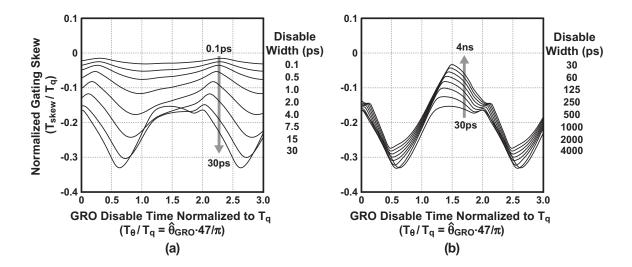

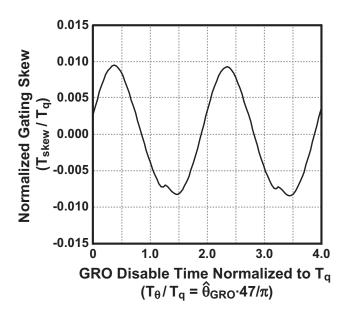

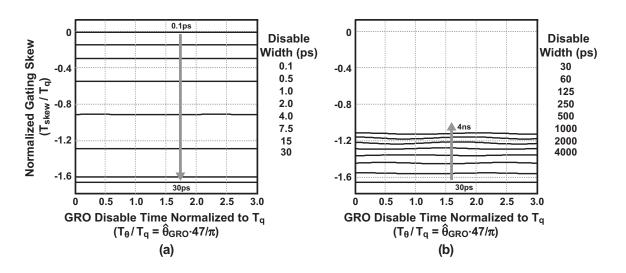

| 3-8  | Gating skew vs. GRO phase for stepped disable widths                                  | 5 |

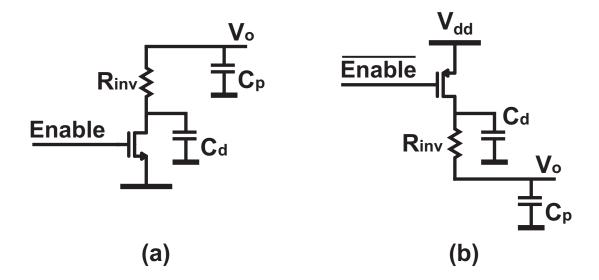

| 3-9  | Schematic depicting two time constants present in the charge redis-                   |   |

|      | tribution within a delay element whose output is in transition at the                 |   |

|      | disable time                                                                          | 5 |

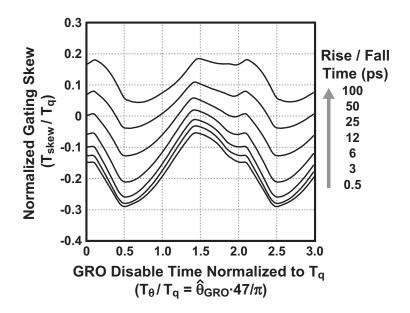

| 3-10 | Gating skew vs. GRO phase for stepped rise / fall times                               | 5 |

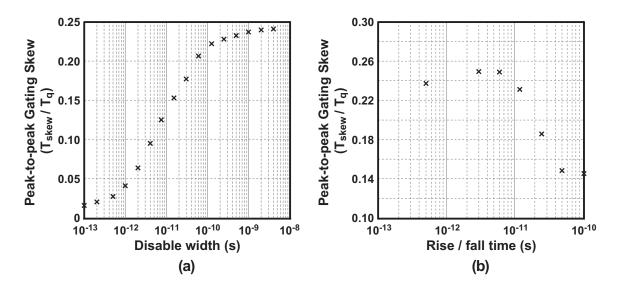

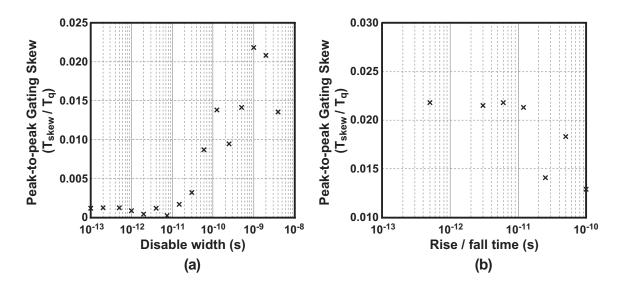

| 3-11 | Peak-to-peak gating skew vs. disable width and rise / fall time                       | 5 |

| 3-12 | Simulated deadzones in the DC GRO-TDC transfer curve                                  | 5 |

| 3-13 | Illustration of the problem in using resistive interpolation for the GRO              | 6 |

| 3-14 | A GRO topology with digital interpolation                                             | 6 |

| 3-15 | Coupled oscillators used to reduce the effective delay per stage                      | 6 |

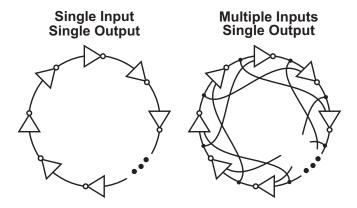

| 3-16 | Basic concept of using multiple inputs for each delay stage                           | 6 |

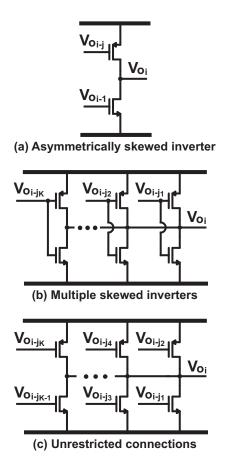

| 3-17 | Techniques to reduce effective delay by modifying the standard inverter               | 6 |

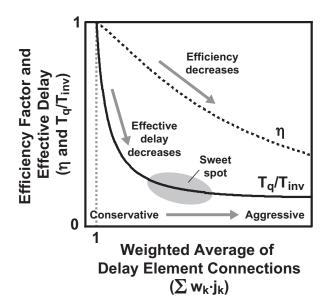

| 3-18 | Example for optimizing multi-path oscillator resolution                               | 6 |

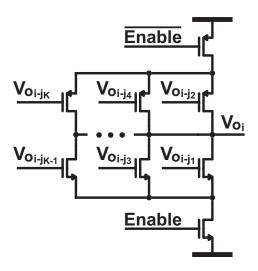

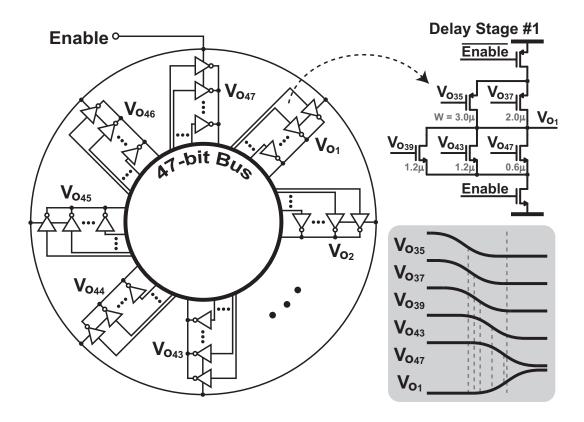

| 3-19 | Delay cell topology for the proposed gated ring oscillator                            | 7 |

| 3-20 | Schematic of the proposed multi-path GRO                                              | 7 |

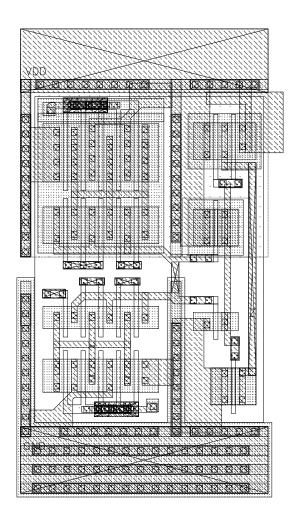

| 3-21 | Inverter delay cell layout for the prototype GRO                                      | 7 |

| 3-22 | Delay cell layout floorplan for the prototype multi-path GRO                          | 7 |

| 3-23 | Simulated transient voltages of the multi-path delay element outputs                  | 7 |

| 3-24 | Concept of how the overlapping skew from positive and negative tran-                  |   |

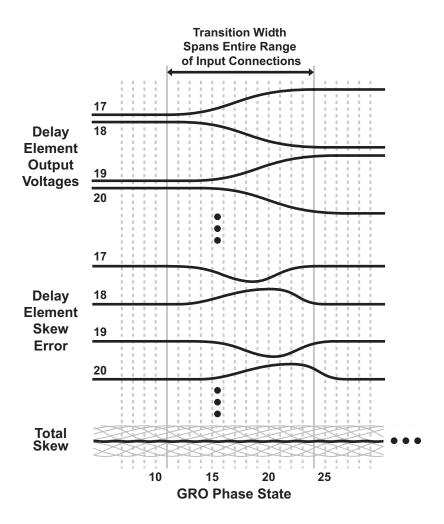

|      | sitions for a multi-path GRO significantly reduces the total skew                     | 7 |

| 3-25 | Multi-path GRO skew vs. phase for typical conditions                                  | 7 |

| 3-26 | Multi-path GRO skew vs. phase for stepped disable widths                              | 7 |

| 3-27 | Multi-path GRO peak-to-peak skew vs. disable width and rise / fall        |     |

|------|---------------------------------------------------------------------------|-----|

|      | time                                                                      | 78  |

| 4-1  | Using two counters for each output stage to keep track of the total       |     |

|      | number of phase transitions                                               | 82  |

| 4-2  | Double-counting transitions in the GRO measurement                        | 82  |

| 4-3  | Basic concept of calculating the GRO-TDC output by differentiating        |     |

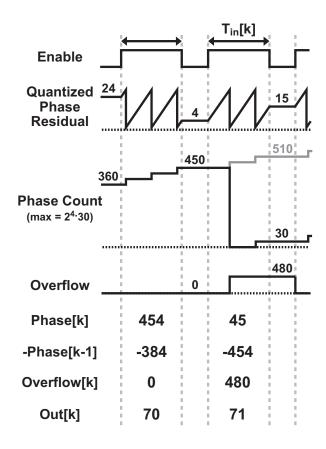

|      | phase                                                                     | 85  |

| 4-4  | Chart showing the logical states of a standard 15-stage ring oscillator   |     |

|      | for each of the 30 possible discrete phase states                         | 86  |

| 4-5  | Accomodating a counter with a limited range                               | 87  |

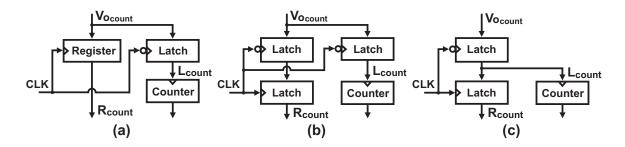

| 4-6  | A potential phase error when the oscillator state is determined by both   |     |

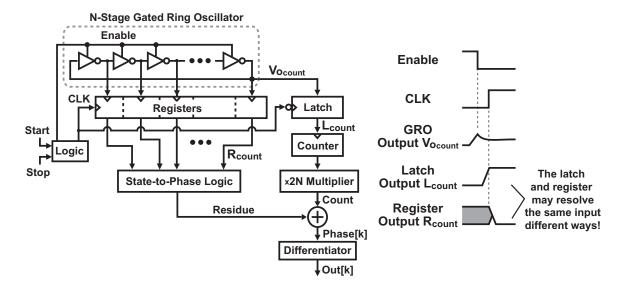

|      | registers and counters                                                    | 88  |

| 4-7  | Combining register and latch functions into a single element $\dots$ .    | 88  |

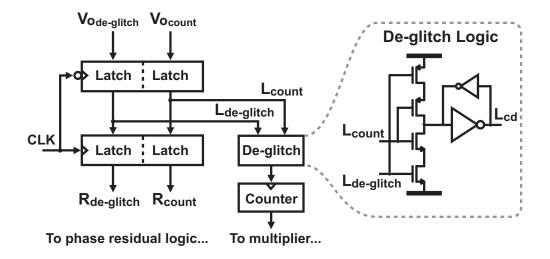

| 4-8  | Implementation of a de-glitch circuit that achieves hysteresis by relying |     |

|      | on the sequence of oscillator states                                      | 90  |

| 4-9  | Overall block diagram of efficient and robust phase measurement tech-     |     |

|      | nique for an inverter-based GRO                                           | 90  |

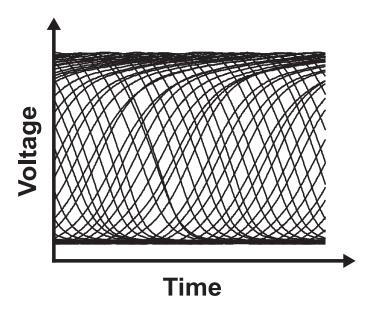

| 4-10 | Simulated transient voltages of the multi-path delay element outputs      |     |

|      | when mismatch is included                                                 | 92  |

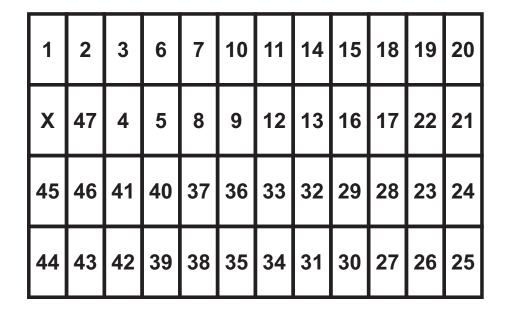

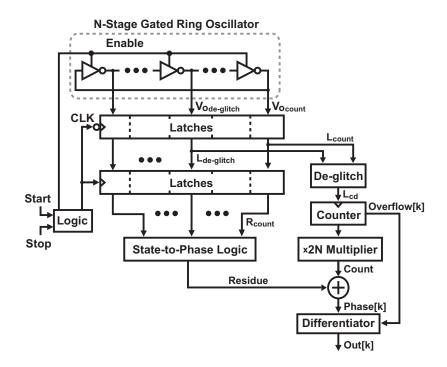

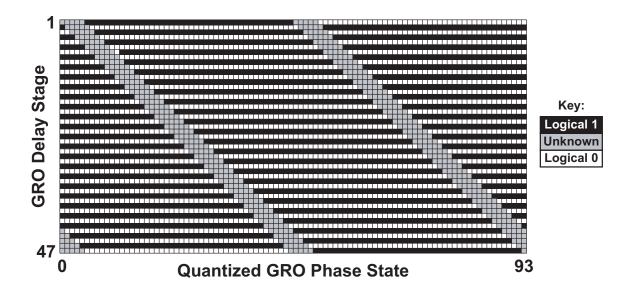

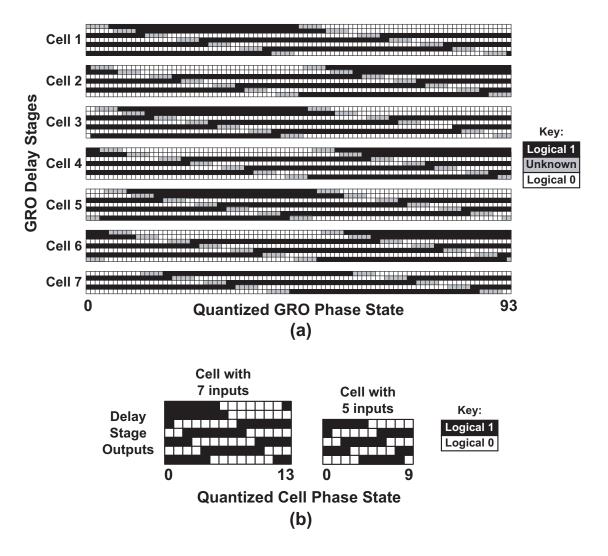

| 4-11 | Logical states of the 47-stage multi-path oscillator for each of the 94   |     |

|      | possible quantized phase states                                           | 93  |

| 4-12 | A geometric view of an example multi-path GRO state                       | 94  |

| 4-13 | Re-arranging the logical states of the multi-path GRO into groups that    |     |

|      | correspond to the 7 measurement cells                                     | 95  |

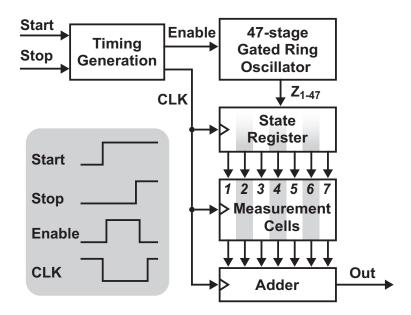

| 4-14 | Overall system block diagram for the proposed 47-stage multi-path         |     |

|      | GRO-TDC                                                                   | 96  |

| 5-1  | Microphotograph of a multi-path GRO-TDC chip                              | 100 |

| 5-2  | A method to create a low-noise input signal for the GRO-TDC testing       | 101 |

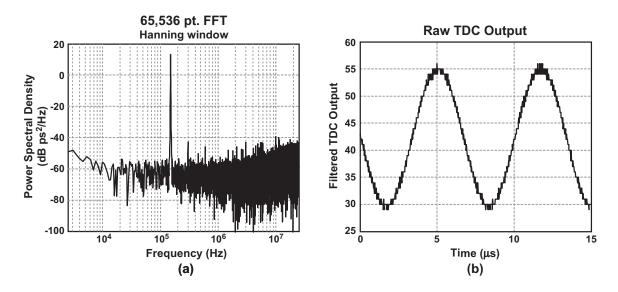

| 5-3  | Measured 65,536-pt. FFT of an inverter-based GRO-TDC output               | 102 |

| 5-4  | An example of non-linear behavior in the inverter-based GRO-TDC .             | 103 |

|------|-------------------------------------------------------------------------------|-----|

| 5-5  | Measured deadzone behavior of the inverter-based GRO-TDC $$                   | 103 |

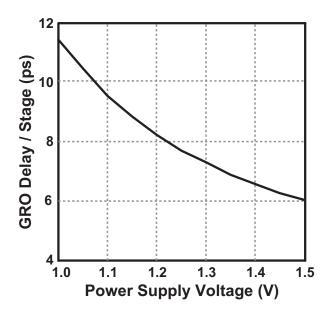

| 5-6  | Measured delay per stage for the multi-path GRO vs. power supply              |     |

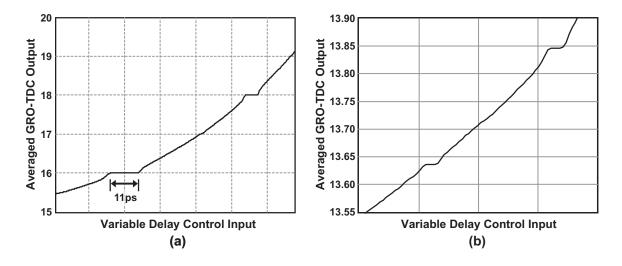

|      | voltage                                                                       | 105 |

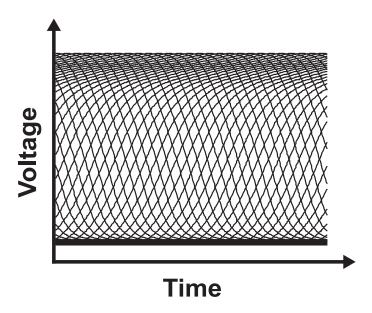

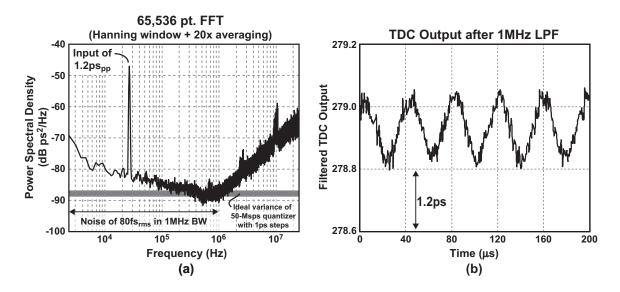

| 5-7  | Measured GRO-TDC output for a 1.2ps $_{pp},26kHz$ input signal $$             | 107 |

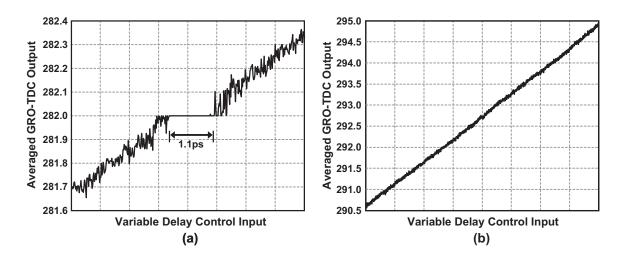

| 5-8  | Measured deadzone behavior of the multi-path GRO-TDC $$                       | 108 |

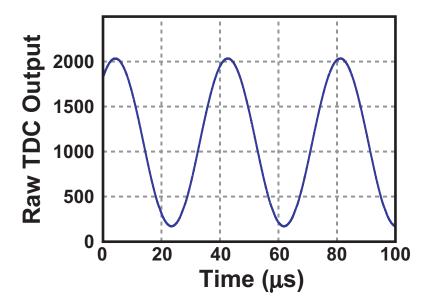

| 5-9  | Raw measured GRO-TDC output for a 26kHz input signal with an                  |     |

|      | amplitude near full-scale                                                     | 109 |

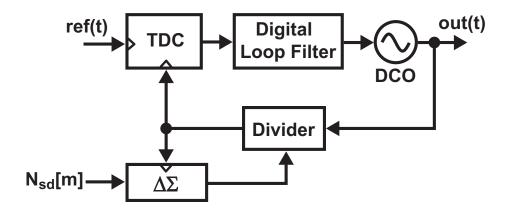

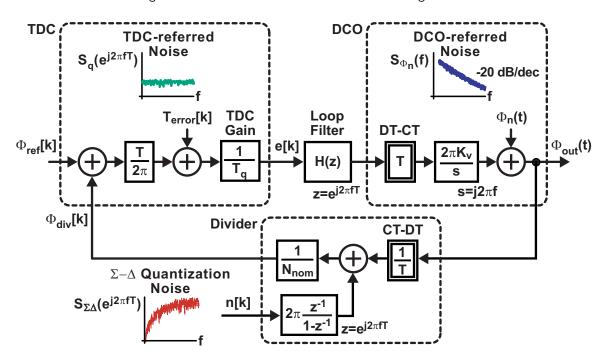

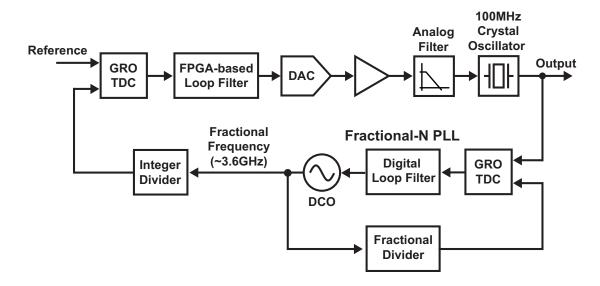

| 6-1  | Basic architecture of a fractional-N digital PLL                              | 114 |

| 6-2  | A general model for the fractional-N digital PLL                              | 114 |

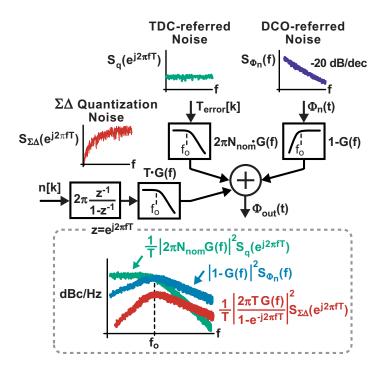

| 6-3  | Transfer functions for the three primary contributions to the digital         |     |

|      | PLL phase noise                                                               | 115 |

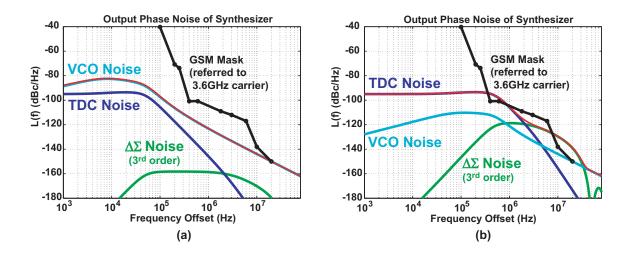

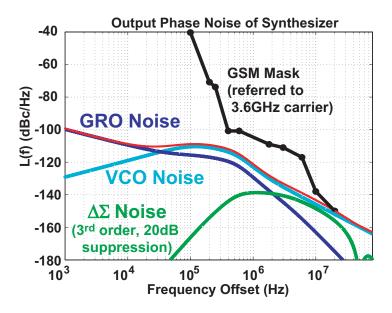

| 6-4  | Calculated phase noise of a digital PLL with 20ps TDC resolution $$ . $$      | 116 |

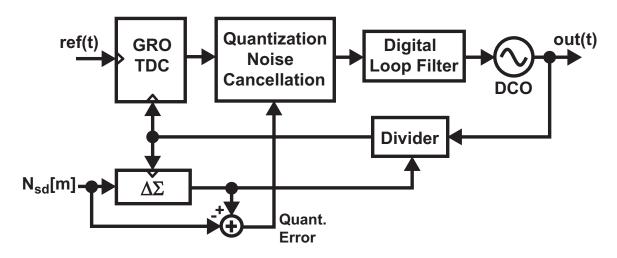

| 6-5  | A fractional-N digital PLL using the GRO-TDC and quantization noise           |     |

|      | cancellation                                                                  | 116 |

| 6-6  | Calculated phase noise of a digital PLL with GRO-TDC $\ \ldots \ \ldots$      | 117 |

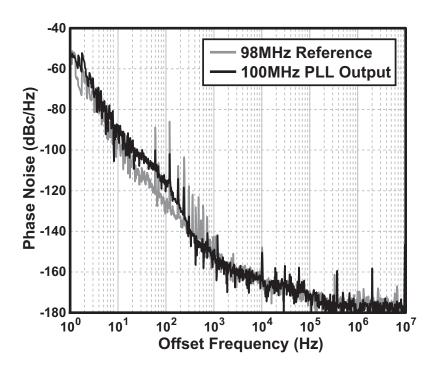

| 6-7  | Measured output phase noise from the prototype $3.6\mathrm{GHz}$ fractional-N |     |

|      | digital PLL using the GRO-TDC $\ \ldots \ \ldots \ \ldots \ \ldots$           | 118 |

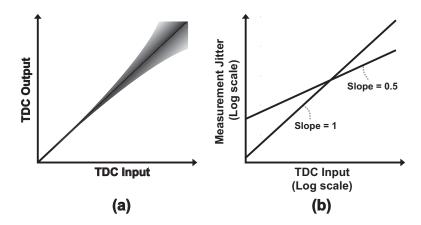

| 6-8  | The relationship between the magnitude of the TDC input and the ran-          |     |

|      | dom measurement error due to thermal and 1/f noise. (a) depicts the           |     |

|      | TDC input / output transfer characteristic, and (b) generally relates         |     |

|      | the statistical measurement jitter to the TDC input                           | 120 |

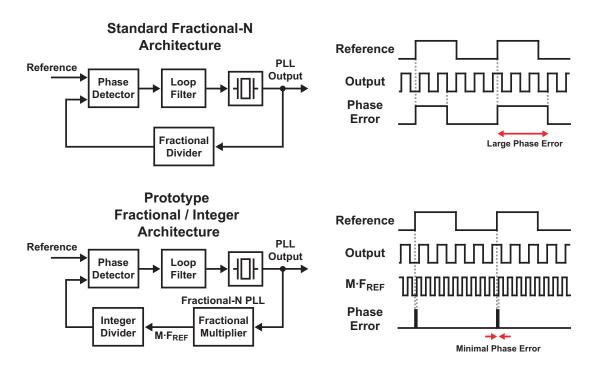

| 6-9  | Concept behind the proposed fractional / integer synthesizer that min-        |     |

|      | imizes the length of time input into the GRO-TDC $$                           | 121 |

| 6-10 | Prototype implementation of the fractional $/$ integer synthesizer $$ . $$ .  | 122 |

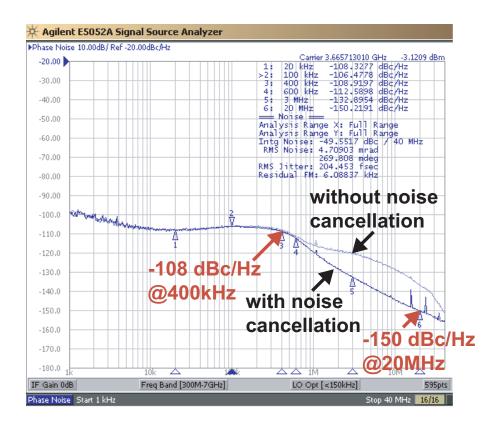

| 6-11 | Measured 100MHz phase noise of the prototype fractional $/$ integer           |     |

|      | synthesizer                                                                   | 123 |

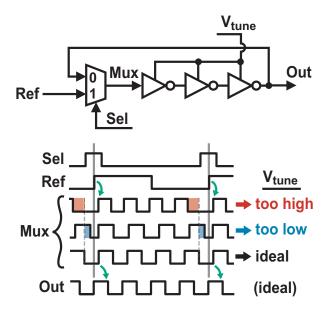

| 6-12 | Concept of a multiplying delay-locked loop                                    | 124 |

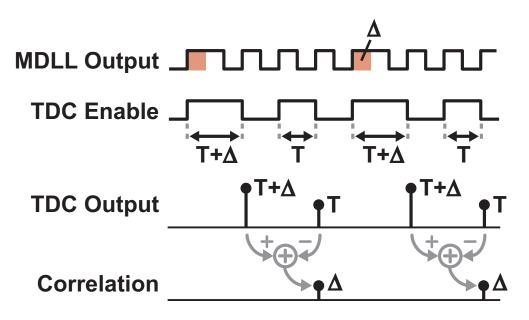

| 6-13 | Correlation of spurs to period measurements                                   | 125 |

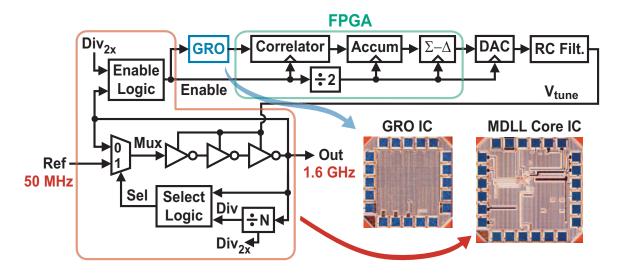

| 6-14 | A block diagram of the implemented MDLL prototype                                     | 126 |

|------|---------------------------------------------------------------------------------------|-----|

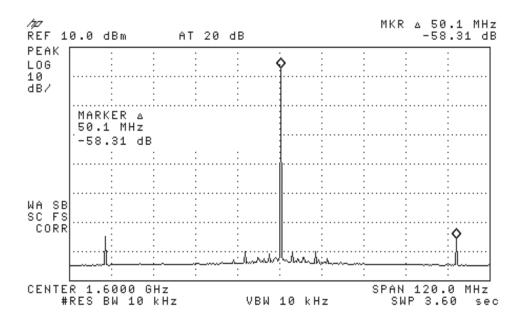

| 6-15 | Measured -58dBc spurious performance from the MDLL prototype                          | 126 |

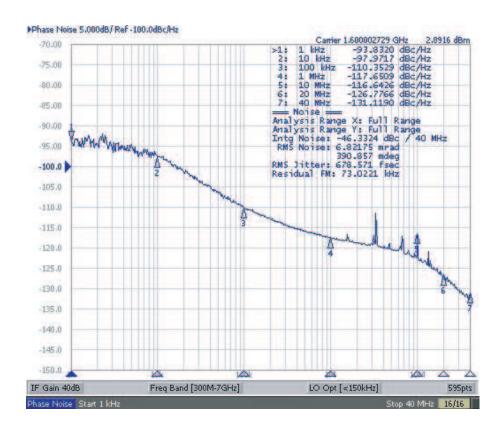

| 6-16 | Measured MDLL phase noise at 1.6GHz output frequency                                  | 127 |

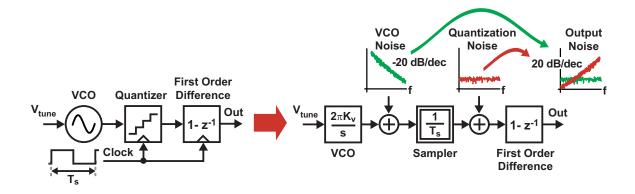

| 7-1  | Simple VCO-based ADC                                                                  | 130 |

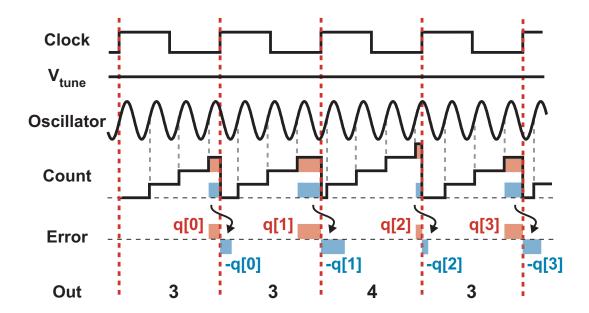

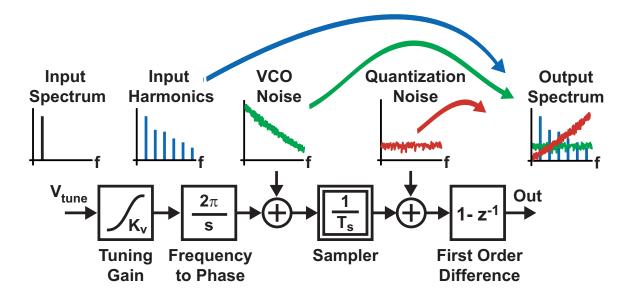

| 7-2  | First-order noise shaping of a classical VCO-based ADC                                | 131 |

| 7-3  | Improved resolution by counting positive and negative transitions of a                |     |

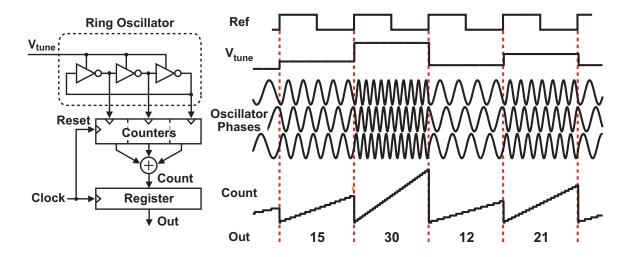

|      | multi-phase VCO                                                                       | 132 |

| 7-4  | High-speed multi-phase VCO frequency measurement                                      | 133 |

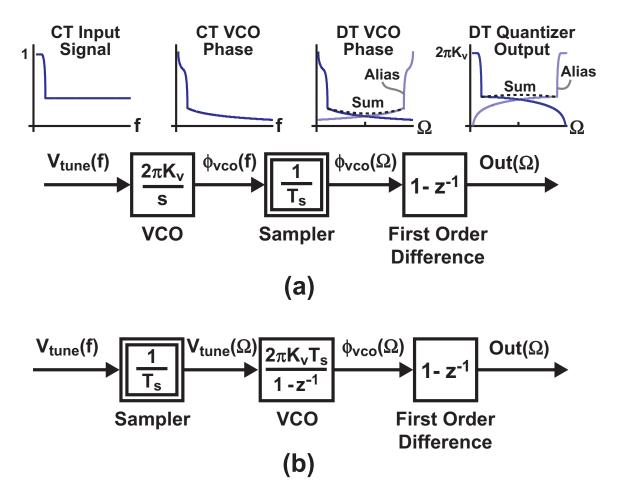

| 7-5  | Block diagram model and corresponding linearized frequency domain                     |     |

|      | model of the VCO-based quantizer                                                      | 135 |

| 7-6  | View of an example spectrum as it passes through the VCO-based                        |     |

|      | quantizer. (a) shows the mixed-mode view with both CT and DT                          |     |

|      | spectra, and (b) shows the DT linear model with the sampler moved                     |     |

|      | to the front-end $\ldots$                                                             | 137 |

| 7-7  | Behavioral model illustrating the VCO quantizer non-linearity                         | 139 |

| 7-8  | Behavioral simulation results of an example VCO-based quantizer $$ . $$ .             | 140 |

| 8-1  | $\Sigma\Delta$ feedback to suppress VCO linearity and quantization errors $\ .\ .\ .$ | 144 |

| 8-2  | Utilizing VCO for implicit barrel shift DEM of DAC elements                           | 145 |

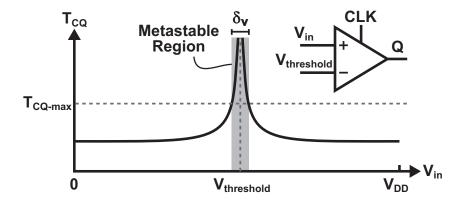

| 8-3  | Dependence of comparator clock-to-Q time on input voltage                             | 146 |

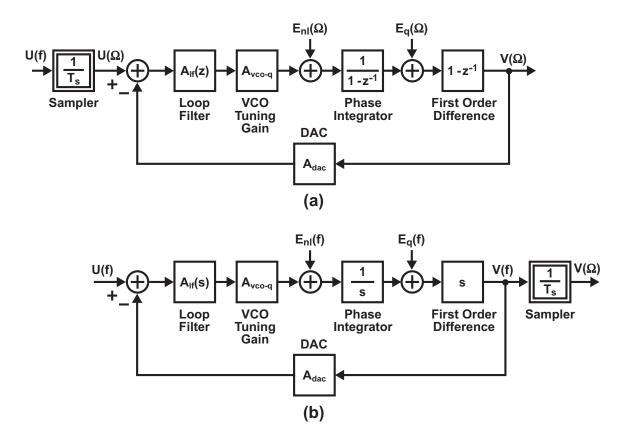

| 8-4  | A model in discrete-time (a) and continuous-time (b) for the VCO-                     |     |

|      | based quantizer $\Sigma\Delta$ ADC with non-linearity error $E_{nl}$ and quantization |     |

|      | error $E_q$                                                                           | 150 |

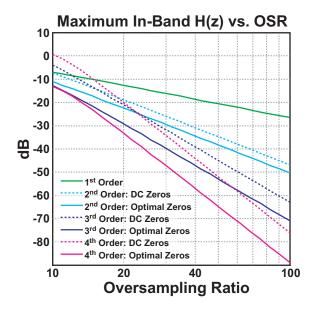

| 8-5  | Maximum in-band $ H(z) $ for a lowpass modulator across oversampling                  |     |

|      | ratio and loop order. The zeros are placed either at DC (dashed line)                 |     |

|      | or at locations optimal for the oversampling ratio (solid line)                       | 151 |

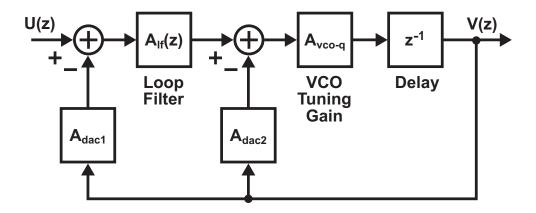

| 8-6  | Model for the prototype ADC including excess loop delay and a minor                   |     |

|      | compensation loop                                                                     | 153 |

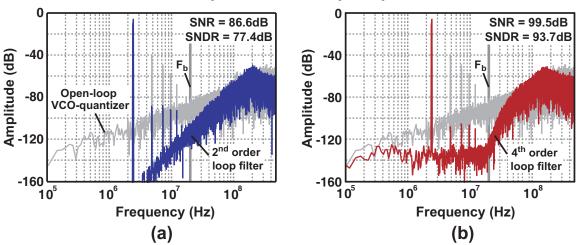

| 8-7  | Behavioral simulation results of an example VCO-based quantizer $\Sigma\Delta$ |     |

|------|--------------------------------------------------------------------------------|-----|

|      | ADC with (a) $2^{nd}$ order loop filter with NTF zeros at DC and (b) $4^{th}$  |     |

|      | order loop filter with optimized zeros for $F_b = 20 \mathrm{MHz}$             | 154 |

| 9-1  | Block diagram of the proposed ADC                                              | 158 |

| 9-2  | Geometric view of the proposed 31-level combined VCO quantizer/DEM $$          |     |

|      | and DAC $\hdots$                                                               | 160 |

| 9-3  | Tuning characteristic for the proposed VCO-quantizer                           | 161 |

| 9-4  | Schematic and operation of (a) $DAC_1$ and (b) $DAC_2$                         | 163 |

| 9-5  | Schematic of the fully differential ADC loop filter                            | 165 |

| 9-6  | Operational amplifier schematic                                                | 165 |

| 10-1 | A microphotograph of the VCO-based ADC                                         | 168 |

| 10-2 | SNR/SNDR vs. input amplitude                                                   | 169 |

| 10-3 | 190,190 point Hanning FFT normalized to an LSB                                 | 171 |

# List of Tables

| 3.1  | Details of the prototype GRO inverter delay cell               | 72  |

|------|----------------------------------------------------------------|-----|

| 4.1  | Truth table for the de-glitch logic                            | 89  |

| 4.2  | Assignment of delay element outputs to measurement cell inputs | 96  |

| 5.1  | Summary of multi-path 11-bit GRO-TDC measured performance      | 110 |

| 5.2  | Comparison with published TDC                                  | 110 |

| 10 1 | Summary of VCO-based ADC measured performance                  | 168 |

|      | Comparison with published high-speed CT ADC                    |     |

# Chapter 1

### Introduction

#### 1.1 Area of focus

As device characteristics for analog applications are expected to steadily degrade in future CMOS processes, there is increasing interest in developing new mixed-signal circuit architectures that better leverage digital circuits to improve analog processing of signals. While this trend has been occurring for some time in the form of digital calibration of analog circuits, it is worthwhile to consider alternate paths toward this goal. One such path is the use of time as a signal domain to perform mixed-signal operations such as digitization of analog signals.

In this context, voltage controlled ring oscillators are circuit elements that are not only very attractive due to their highly digital implementation which takes advantage of scaling, but also due to their ability to amplify or integrate conventional voltage signals into the time domain. In this work, we take advantage of voltage controlled oscillators (VCO) to implement analog- and time-to-digital converters with first-order quantization and mismatch noise-shaping.

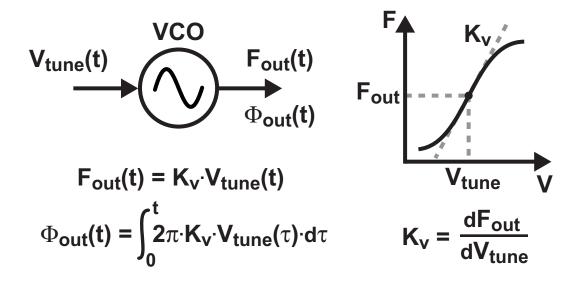

Figure 1-1 depicts the VCO as an element that transforms an analog input voltage into an output signal with binary levels that can be interpreted *either* as frequency or phase. To explain, we first notice that the instantaneous VCO output frequency is directly proportional to the voltage applied to its tuning node. An example of the VCO voltage-to-frequency transfer characteristic is shown on the right side of Figure 1-1,

Figure 1-1 VCO voltage-to-frequency and voltage-to-phase relationships

and defines the slope of the curve,  $K_v$  [Hz/V], as the small-signal voltage-to-frequency gain. Second, we also see that the VCO effectively behaves as a continuous-time (CT) voltage-to-phase integrator. Since the output phase of an oscillating VCO accumulates without end, the VCO voltage-to-phase integration is then ideal in the sense that there is infinite DC gain. Finally, while the phase of the VCO output signal changes continuously, its voltage output toggles between two discrete output levels: high voltage and low voltage. Consequently, the VCO can seamlessly drive other digital blocks with little additional signal conditioning or amplification.

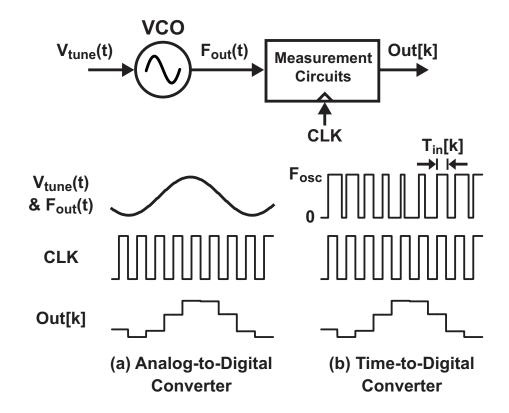

It is well-known that a simple ADC can be formed with a VCO structure by simply adding a frequency measurement capability as depicted in Figure 1-2(a). As we will see, the measurement circuits can be implemented a number of ways, however we can conceptualize this circuit for now as simply counting the number of VCO periods in each sampling clock period. The digital output of the measurement circuit will then correspond proportionally to the input voltage through the  $K_v$  gain factor.

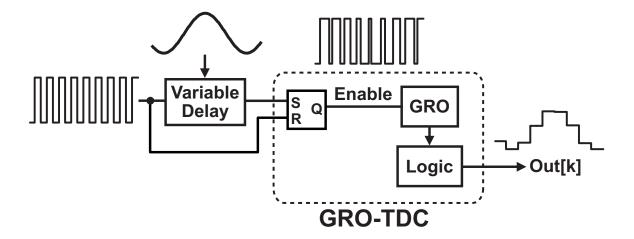

To implement a time-to-digital converter (TDC) with noise-shaping using the VCO structure, we present an oscillator that is enabled during the measurement of an input, and then disabled in between measurements as shown in Figure 1-2(b). Note that in this case the frequency is discrete and ideally toggles between fixed

Figure 1-2 The concept of VCO-based converters: (a) a simple analog-to-digital converter, (b) a gated ring oscillator time-to-digital converter

binary values, 0 and the nominal oscillation frequency, and the analog input  $T_{in}$  is now the length of time that the oscillator is enabled. The measurement circuit again monitors the number of VCO periods or transitions that occur during the sample clock period such that the converter output linearly corresponds with the width of the input signal.

A very interesting aspect to both of these converter architectures is that, despite a digital implementation, the analog quantization error for each sample can actually be saved and passed along to the following measurement. If each sample corrects for the error from the previous sample, then the average quantization error will improve significantly by sampling the same input multiple times. In fact, we can say that properly preserving and accounting for this error will result in first-order noise-shaping in the frequency domain.

Although first-order noise-shaping is well-known and can be achieved in a relatively straight-forward manner for the ADC of Figure 1-2(a), to our knowledge

noise-shaping for a TDC has not been previously demonstrated. In order to practically achieve good noise-shaping performance for the TDC of Figure 1-2(b), the quantization error must be preserved during the time that the oscillator is disabled. In fact, holding the phase state of a VCO represents a new concept outside of the typical operating conditions for an oscillator. We therefore explore the key issues in transferring this error, and present key details of a multi-path oscillator topology that is able to significantly improve raw resolution and at the same time accurately preserve the quantization error from measurement to measurement.

An 11-bit, 50Msps prototype time-to-digital converter (TDC) using a multi-path gated ring oscillator with 6ps of delay per stage demonstrates over 20dB of 1st-order noise shaping. At frequencies below 1MHz, the TDC error integrates to  $80 fs_{rms}$  for a dynamic range of 95dB with no calibration of differential non-linearity required. The  $157x258\mu m$  TDC is realized in  $0.13\mu m$  CMOS and operates from a 1.5V supply.

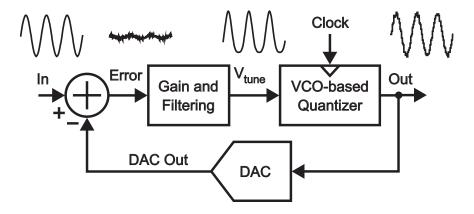

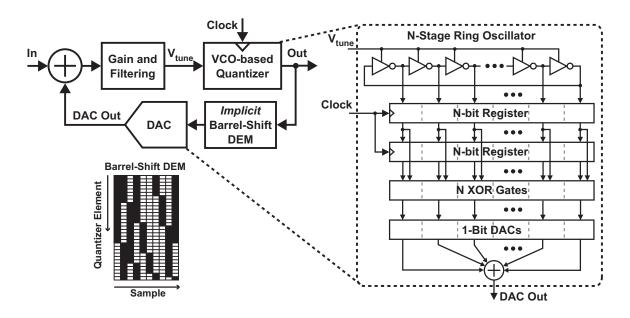

The use of VCO-based quantization within continuous-time (CT)  $\Sigma\Delta$  ADC structures is also demonstrated, with a custom prototype in 0.13 $\mu$ m CMOS showing measured performance of 86/72dB SNR/SNDR with 10MHz bandwidth while consuming 40mW from a 1.2V supply and occupying an active area of 640 $\mu$ m X 660 $\mu$ m. A key element of the ADC structure is a 5-bit VCO-based quantizer clocked at 950 MHz which we show achieves first-order noise-shaping of its quantization noise. The quantizer structure allows the second order CT  $\Sigma\Delta$  ADC topology to achieve third order noise shaping, and direct connection of the VCO-based quantizer to the internal DACs of the ADC provides intrinsic dynamic element matching (DEM) of the DAC elements.

#### 1.2 Primary contributions

In regard to a VCO-based time-to-digital converter, the primary contributions of this thesis are:

• The introduction of a gated ring oscillator topology that, when used in a timeto-digital converter, can achieve first-order noise-shaping of quantization and mismatch error

- The analysis of errors due to gating an oscillator that can fundamentally limit noise-shaping performance

- The mitigation of these errors with a multi-path ring oscillator topology that linearizes the gating operation and reduces the effective delay per stage to a small fraction of an inverter delay

- The presentation of techniques to efficiently and accurately measure the phase of a multi-path ring oscillator

- The verification of first-order noise-shaping with measured results of a prototype gated ring oscillator TDC

To our knowledge, the gated ring oscillator time-to-digital converter presented in this work is the first TDC to demonstrate noise-shaping of analog quantization and mismatch error for non-adjacent measurement intervals. Further, compared with other reported TDC, the prototype described in this work is very competitive in regard to important metrics such as dynamic range, power, and area.

Another contribution of this work is the analysis of the performance advantages, limitations, and tradeoffs for an oversampled VCO-based quantizer, along with the demonstration of these considerations within a high-speed continuous time  $\Sigma\Delta$  ADC. The idea of using a VCO for voltage quantization within a  $\Sigma\Delta$  ADC has been presented multiple times [28,39], and in fact the architecture chosen independently for this work was originally disclosed in [39]. However, while the ideas for using VCO in a  $\Sigma\Delta$  ADC have been known for many years, this work provides measurement results that justify the consideration of VCO-based quantizers in  $\Sigma\Delta$  ADC. Improvements are also discussed that may significantly improve these results, although the achieved performance is at present competitive with other state-of-the-art ADC architectures.

Together, these contributions demonstrate the utility of ring oscillator-based quantizers in achieving or advancing state-of-the-art performance for the time- and analog-to-digital converters.

#### 1.3 Thesis overview

The thesis is divided into two main parts; the first half focuses on the gated ring oscillator time-to-digital converter in Chapters 2-6, and the second half addresses VCO-based analog-to-digital conversion in Chapters 7-10. For both sections, we will summarize previous work in the area, analyze and discuss the various issues that must be addressed to achieve high resolution, and present prototype implementations along with measurement results. Chapter 11 concludes the thesis with a few general remarks.

The first half of the thesis begins with Chapter 2, where we provide a background on time-to-digital converters and motivate the gated ring oscillator topology of this work. To accomplish this, we discuss historical TDC trends, describe a number of modern TDC architectures, and consider the benefits of oversampling before explaining the fundamental concept of the GRO-TDC. In Chapter 3, we examine the accuracy with which a digital GRO implementation can preserve analog signals from one measurement to the next, and present the multi-path oscillator topology that addresses these concerns. The measurement of the GRO with precise, efficient circuitry is discussed in Chapter 4, and measurement results are shown in Chapter 5. To conclude the first half of the thesis, we briefly outline methods to utilize the GRO-TDC in a number of system applications.

Chapter 7 initiates the second half of the thesis by looking at the advantages and shortcomings of a simple VCO-quantizer. The quantizer is then placed within a  $\Sigma\Delta$  ADC in Chapter 8 to improve its linearity performance, and where a few unique properties of the VCO-quantizer can be leveraged at the architectural level. System and circuit-level details of the prototype  $\Sigma\Delta$  ADC are described in Chapter 9, and the presentation of measurement results along with a discussion are included in Chapter 10.

# Chapter 2

# Background on Time-to-Digital Converters

#### 2.1 Introduction

Accurate measurement of time has had a critical role in the development of science throughout history, starting with the earliest examples of analog clocks based on solar motion and water flow, and including the most accurate caesium resonators available today. As a subset of time-keeping technology, time-to-digital converters (TDC), or time-interval meters (TIM), allow for precise measurement of the time between two events. Historically, TDC have had significant application in experimental physics. For example, in the nuclear physics community, measurements of mean lifetime, particle identification, and time-of-flight require precise TDC, and many of the early integrated circuit TDC addressed such needs [53]. Today, TDC continue to serve an important role not only in experimental applications, but also in commercial time-of-flight applications such as laser rangefinding and positive electron tomography (PET) medical imaging technology [70].

A relatively new application for TDC that has emerged is closed-loop timing systems that are fully integrated in silicon technology. Since advanced CMOS processes have begun to offer extremely compact, robust, and flexible processing power, many applications have begun to replace traditional analog signal processing blocks with

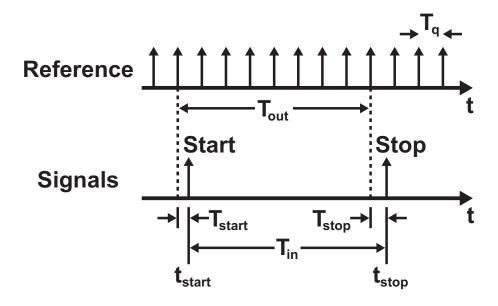

Figure 2-1 Reference and signal pulses vs. time

digital signal processing. Such a shift in architectural design places a relatively increased burden on the mixed-signal interface, especially in terms of converter performance. For systems that require precise control or alignment of timing signals, such as phase-locked loops (PLL), delay-locked loops (DLL), and clock and data recovery (CDR) circuits, the TDC is a fundamental element that can bridge the gap between the continuous-time analog domain and the discrete-time digital domain.

Considering that there is an extensive history of TDC prior to the development of digital PLL, it is useful to understand how today's state-of-the-art TDC technology relates to older ideas that have been around for some time. In fact, a review of the historical developments of TDC over the past 50 years or more reveals that, while technology has seen a tremendous change from vacuum tubes and ferrite pot-core transformers to present-day advanced CMOS, the concepts and techniques for dividing time into measureable intervals have remained remarkably the same. Given this context, although it is possible to think of TDC architectures in terms of implementation details, it is also instructive to think of the architectures in a conceptual manner. In this way, we can both understand current practice and, at the same time, shape the future efforts in TDC development by considering how these simple but powerful ideas best can be used within a new, yet undefined, component technology.

We then examine Figure 2-1, which is a picture describing the general operation of a TDC that can serve as an entry point into the discussion of many different TDC architectures and ideas. The figure, while modified slightly for our purposes, is basically equivalent to Figure 1 from Baron's 1957 original manuscript on the Vernier technique [4]. From the figure we see that the input time interval,  $T_{in} = t_{stop} - t_{start}$ , can be divided up into a number of smaller reference time intervals of nominal length  $T_q$ . An estimate of  $T_{in}$  can be trivially calculated by counting the number of intermediate reference pulses or events (i.e.  $T_{out}[k] = Out[k]T_q$ ), although there is an error to this method at both the beginning and end of the measurement,

$$T_{error}[k] = T_{stop}[k] - T_{start}[k]. \tag{2.1}$$

Given these definitions, we can express the input and output relationship for a TDC as

$$T_{out}[k] = T_{in}[k] - T_{error}[k], \qquad (2.2)$$

or equivalently in terms of the TDC integer output as

$$Out[k] = \frac{T_{in}[k] - T_{error}[k]}{T_a}. (2.3)$$

Since the raw TDC resolution is limited by  $T_q$ , it is not surprising that a great deal of effort over the years has been made in reducing this value, either directly through technology advancement, or effectively by using design techniques, a few examples of which will be covered later in the following section. While these efforts have made significant progress in improving TDC resolution, applications continue to demand the best resolution and/or range than can be achieved in a practical fashion.

For many early TDC applications, and especially for experimental applications, the form factor of the TDC was less important than achieving high-resolution and accuracy. As a result, many of the best TDC solutions in terms of resolution are large,

<sup>&</sup>lt;sup>1</sup>We should note that within this manuscript we find that Baron "recognizes the fact that the Hughes Research and Development Laboratories, prior to the work described in this report, had fabricated a similar vernier measuring system."

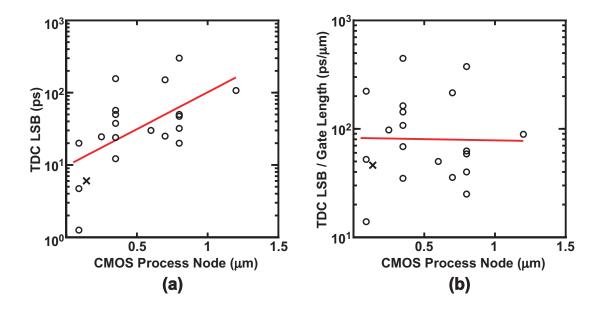

Figure 2-2 Trends of reported time-to-digital converter LSB resolution versus CMOS process technology. (a) depicts the improved resolution (decreased LSB steps) as gate lengths scale, and (b) demonstrates the relatively flat performance of TDC resolution when normalized to gate length

consume significant power, and require complex tuning or calibration. For example, in the dual-conversion approach, classic voltage-domain analog-to-digital converters can be utilized for a TDC by integrating current onto a reference capacitor for each input sample [68], which converts time into voltage before digitization. Although this approach may result in excellent resolution for a particular technology, the architecture is analog-intensive, is not power efficient, and does not take advantage of the ability to resolve digital edges in modern CMOS.

In contrast, TDC constructed with digital CMOS technology have benefited greatly from process feature scaling, since a more advanced process results in not only compact and fully-integrated solutions, but also smaller CMOS gate delays and the accompanying improvement in resolution. Figure 2-2(a) plots reported LSB size for TDC implemented in CMOS over the last decade versus the CMOS technology node (this work is shown with a  $\times$ ), and a best-fit line to the data is also shown [8–10, 13, 18, 19, 27, 29, 30, 34, 37, 43, 44, 46, 48, 56, 66, 71]. We can clearly see from this data evidence that CMOS scaling has indeed resulted in better TDC resolution, and assuming that at least some new process developments are made in the

future, TDC resolution should continue to improve.

On the other hand, Figure 2-2(b) demonstrates that when the LSB size of various TDC are normalized to the minimum transistor gate length in the process<sup>2</sup>, the performance of TDC has been relatively flat. While advancements have certainly been made in adapting TDC architectures for modern CMOS, improvements to the fundamental relationship between gate delay and LSB step size have been difficult to realize.

Certainly one way to interpret this data is to say that the best way to achieve an optimal TDC resolution performance is to wait, i.e. to follow Moore's law until scaling enables better performance with known TDC techniques. While this may be a valid approach for some applications, it does not aid the TDC designer in optimizing resolution performance for a given technology. Given the difficulty in improving the raw resolution in a standard CMOS process, it then becomes important to fully explore techniques such as oversampling to improve effective resolution performance, which is a primary focus of this work.

Moreover, when considering future CMOS TDC and process scaling, it is well known that transistor and parasitic mismatch has become a very real and significant problem for the most advanced technologies [54]. Therefore, while intrinsic delay may continue to decrease in the future, for traditional TDC architectures to benefit from this we also require the accuracy of the delay to improve as well. We will later see that mismatch can be a bottleneck for many TDC architectures. Therefore, achieving high performance in the presence of large delay mismatch is a critical requirement for future TDC that has so far seen little attention at the architectural level compared with the relative efforts to improve raw resolution.

Since we have described some of the basic challenges facing TDC, in the next section we will review some of the state-of-the-art TDC architectures along with their associated performance tradeoffs. This review will lead into the focus of this work, which is a CMOS gated ring oscillator (GRO) TDC. The GRO-TDC makes full

<sup>&</sup>lt;sup>2</sup>Gate propagation delay is often approximated to be proportional to transistor length [81, 82], and therefore normalizing to transistor gate length is a reasonable way to normalize fundamental resolution.

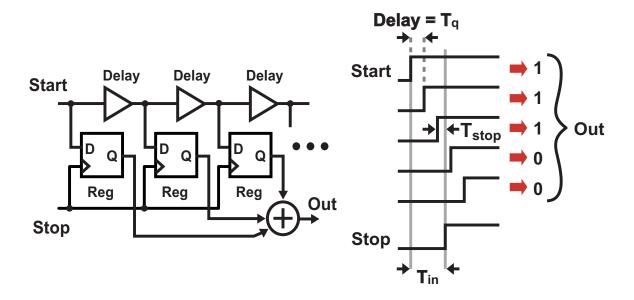

Figure 2-3 Classical delay-chain TDC

use of oversampling to address the issues of limited TDC resolution in the presence of large mismatch, while at the same time achieving a large dynamic range, compact area, and low power consumption.

#### 2.2 TDC with gate-delay resolution

A classic TDC architecture comprised of a chain of delay elements is shown in Figure 2-3 [2, 32], and effectively works by counting the number of sequential inverter delays that occur between two rising signal edges. One very attractive feature of this architecture can be seen immediately in that the TDC can be constructed entirely from standard digital gates, as evidenced by its adoption into the FPGA community [65, 78]. The compact and digital architecture offers a moderate performance, and has been proved to be commercially viable for some digital PLL applications in the wireless industry [66].

To explain its operation, the rising edge of the start signal, which represents the first event, is successively delayed by a series of inverter gates (polarity is ignored throughout for simplicity), each with delay  $T_q$ . The outputs from each of these inverters are input to a register, which is clocked with the rising edge of the stop signal

Figure 2-4 A cyclic TDC based on re-using delay elements

representing the second event. A thermometer code is then generated at the register output, which corresponds to the number of delay elements that have transitioned within the measurement interval  $T_{in}[k]$ . The TDC output Out[k] is then simply calculated as the sum of the thermometer code, and is related to the input by Equation 2.3, where the overall error can be described in this case as

$$T_{error}[k] = T_{stop}[k]. (2.4)$$

Although the delay-chain architecture offers a simple TDC with moderate performance, an important limitation to consider is the high cost for increasing its range. Increasing the dynamic range of the delay-chain TDC requires a *linear* increase in the number of delay elements, which similarly increases the power consumption and decreases the maximum sampling rate.

A simple solution to the limited range of the delay-chain TDC is to wrap or fold the end of the chain back to the beginning through a multiplexer that is controlled by digital logic, as shown in Figure 2-4. The multiplexer selects the start signal during the beginning of each time interval, and after this start signal has occured then quickly switches to select the end of the delay-chain so that the subsequent edge transitions rotate around the ring. This technique allows each of the delay elements to be used multiple times per measurement, and the TDC output is simply found by counting and summing all of the delay element transitions that occur during  $T_{in}$ . Compared to the delay-chain TDC, the cyclic TDC core does not scale up at all with larger range, and the counters will only scale with the logarithm of range.

Asymmetry in the delay-chain structure due to the multiplexer increases the mismatch for that particular element, which degrades the differential non-linearity performance. Techniques to match the multiplexer delay to that of a delay element can be used, such as incorporating a multiplexer with fixed connections in each of the delay elements [23]. In terms of integral non-linearity, the cyclic TDC has better performance than the delay-chain TDC for large input signals due to the periodic use of delay elements.

While the TDC range can be improved with the simple cyclic TDC, a more problematic issue that has not been addressed is the coarse resolution, which is limited to a minimum inverter delay in the process. Although over time technology scaling will improve the intrinsic delay, the mismatch of delay elements is expected to get worse. Additionally, as mentioned in the preceding section, physical limitations due to TDC thermal and 1/f noise will continue to be out-of-reach for resolutions limited by a gate-delay. Therefore, an important problem to consider is how  $T_q$  of the simple delay-chain architecture can be divided into smaller intervals in order to significantly improve TDC resolution.

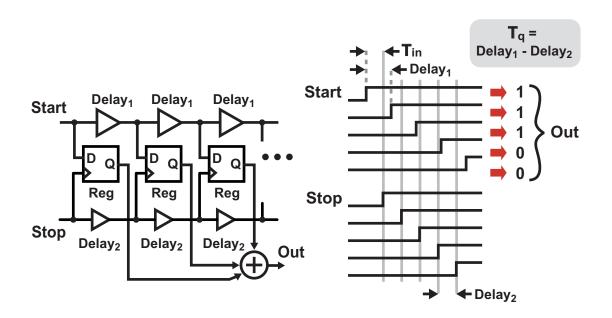

#### 2.3 TDC with sub-gate-delay resolution

The Vernier delay technique [4] is one of the older techniques for time digitization that has been adapted for improving the resolution of digital CMOS TDC [13,55,57], and has been widely documented in the literature. As shown in Figure 2-5, the concept is to effectively stretch the input time interval  $T_{in}$  by delaying both the start and stop signals with delay-chains. What defines the resolution in this case is not the absolute rate of transitions (gate-delay being equal to the number of transitions per second), but the relative rate of transitions. As a result, the effective resolution of the Vernier TDC is found to be the difference of the two delays, or more specifically,

Figure 2-5 An Vernier TDC that effectively amplifies the input time interval

$T_q = Delay_1 - Delay_2.$

Given this result, the Vernier technique may appear to be able to substantially improve a TDC resolution. However, there are a number of issues to consider that practically limit the resolution improvement to a factor of 4-10. Specifically, the same issues that are found in the simple delay-chain TDC (e.g. range, sensitivity to mismatch) are present in the Vernier TDC, except that, along with the resolution, the magnitude of the problems have also been amplified. Although the Vernier delay elements may be tuned to match a fixed offset and calibrated at the system level, such techniques are both cumbersome and dependent on system-level architecture design [76].

To reduce the size of practical Vernier TDC, various dual step architectures based on Vernier techniques have been proposed [27,56,57], as shown in Figure 2-6. These architectures often have a simple delay-chain TDC (Figure 2-3) as the first stage, and then further refine the initial measurement by amplifying the residual error and then passing it to a second, higher resolution Vernier TDC. Another dual step technique that amplifies time error using the metastability property of digital gates has also been proposed, and in this case a larger resolution improvement up to a factor of 20 is reported [34].

Figure 2-6 A dual-step TDC that incorporates both the delay-chain and Vernier techniques

Although the range for these architectures is larger than what would be achieved for a single-step TDC using the same resolution improvement techniques, the fundamental range versus size tradeoff does not improve compared with the simple delay-chain TDC discussed earlier. Interestingly, a cyclic architecture similar to Figure 2-4 may be used to significantly increase the range of the single or dual-step Vernier TDC [57]. In this case, the decoding logic and calibration become more complicated due to the many logical states that are supported.

Another technique to improve TDC resolution below that of a gate-delay is to interpolate between the input and output signals of a digital gate. Figure 2-7 illustrates this concept using a resistive divider, where the undriven nodes are taken to be the average of the delay element input and output signals. The operation of averaging creates a new intermediate signal with a transition that effectively divides the gate-delay into two smaller intervals. All of the new signals must be registered appropriately, which increases the TDC size, but again a cyclic architecture can be utilized to mitigate this issue [23]. The improvement in resolution for the interpolation architecture over the gate-delay is similar to that of the Vernier architecture, and is practically limited by the non-linear impedances of the delay elements during

Figure 2-7 An analog interpolating TDC that creates transitions with sub-gate-delay spacing

Figure 2-8 A digital technique for creating transitions with sub-gate-delay spacing

the switching transients.

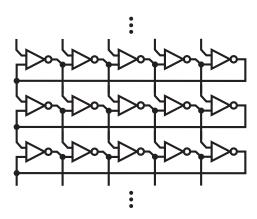

The implementation of the interpolation architecture is not limited to resistive ladders, and can also be efficiently realized with digital gates if the output signals are allowed to be driven by more that one delay element. As shown in Figure 2-8, the same averaging effect can be achieved by connecting the outputs of two delay elements in parallel, while the two delay element inputs are staggered in time. The result from this parallel connection is that the output impedances from both delay elements are averaged together, which then reduces the effective delay per stage. Although this

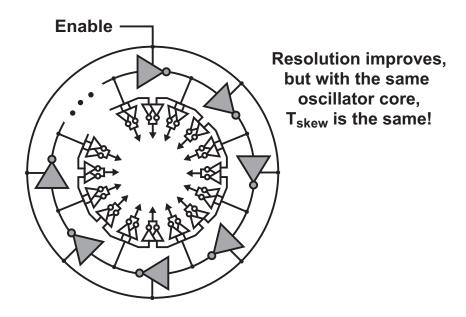

architecture can also be expanded into a cyclic TDC, achieving a significant improvement in resolution requires more than two delay elements to be connected in parallel, which then increases the complexity of the multiplexer significantly. Nonetheless, we will later see in Chapter 3 that these techniques can be modified when constructing an oscillator-based TDC, and can in fact be to be quite useful.

For each of the Nyquist TDC architectures described so far, we have seen that significant effort is required to reduce the TDC resolution below that of a gate-delay, and in each case the cost for doing so is increased complexity, area, and/or mismatch. Another common thread to these converters is that there is a deterministic mapping from a given input signal onto a series of delay elements. Since we know that significant element-to-element delay variations due to mismatch cause quantization errors that are non-linear, calibration is very much required for such converters that hope to have resolution far below that of a gate-delay [23, 34, 66]. In a practical implementation, although calibration does generally improve resolution performance in the presence of mismatch, it is an added complexity that can significantly increase TDC area and power comsumption. Further, while calibration is quite effective at improving integral non-linearity, it is very difficult to completely remove differential non-linearity errors.

#### 2.4 Oversampling TDC considerations

From the examples described in the previous section, we clearly seek TDC implementations not only with excellent resolution, but also with inherently robust sensitivity to issues such as mismatch. It is in this context that we proceed to consider how oversampling may be used to improve TDC performance.

Oversampling describes the quantization of a signal with fixed bandwidth  $(F_b)$  at a speed  $F_s$  much faster than the Nyquist rate required to reconstruct the original signal without aliasing. Because we often assume that the quantization error,  $T_{error}$ , is random and uniformly distributed over the quantization step, linear system analysis is commonly applied to compute the quantization noise power spectral density (PSD).

Figure 2-9 The DC transfer characteristics for (a) a completely deterministic TDC, (b) a deterministic TDC with small jitter either due to thermal noise or the input, and (c) a TDC with "white" quantization error due to inherent error scrambling or external dithering

Such standard analysis in the frequency domain assumes that the resulting quantization error is spectrally white and that its PSD in discrete time ideally decreases with sampling rate,

$$PSD_{error} = \frac{T_q^2}{12F_s}. (2.5)$$

It is then expected that filtering of the converter output to remove the undesidered bandwidth will also remove a similar proportion of quantization noise, thus realizing the improved signal-to-noise ratio that oversampling can ideally provide.

However, as just mentioned, such analysis depends on the quantization error being random and uniformly distributed over the quantization step, which is not true in general for quantizers with small input signals. As we saw earlier, an important characteristic of the delay-chain TDC is that, since there is no error at the beginning of the measurement (Equation 2.4), the output and error for each measurement are deterministic functions of the input. As a result, the DC transfer characteristic of an ideal delay-chain TDC shown in Figure 2-9(a) reveals a non-linear staircase function. For this class of deterministic converters, there is no inherent scrambling of the TDC error that generally can be used to improve effective resolution through oversampling.

In practice, even for deterministic TDC, there is a small amount of noise from both the input signal and the TDC itself that will round off the edges of this staircase function. As shown in Figure 2-9(b), the resulting DC transfer characteristic is now smoothed somewhat, although the staircase non-linearity can still be evident. In fact, a linear DC transfer characteristic (i.e. a random quantization error) can be achieved in a deterministic quantizer *only* if the input signal is sufficiently large compared to the quantization step size, which includes the situation where the input signal itself is noisy, or if the physical noise internal to the converter is larger than the quantization step size. This condition is illustrated in Figure 2-9(c).

In a closed-loop system such as a PLL, there are certain conditions in which the system may provide such scrambling of the TDC input, for example as it may in a fractional-N  $\Sigma\Delta$  PLL. However, there are many applications to be aware of that do not provide such a dithering. For example, the TDC input for high-performance integer-N PLL limits to a very small range with very little deviation or noise, and a lack of random error in deterministic TDC can be a significant problem. This situation can be compared to the classic dead-zone in an analog phase detector, which is well-known to cause erratic limit-cycle behavior in integer-N PLL.

One solution to this problem is to intentionally modulate the TDC input with a sufficiently noisy signal in order to improve the randomness of the quantization error. Of course, adding unknown noise to a TDC input is a rather poor way to linearize the quantization. Instead, if the "noisy" signal is known and the gain of the TDC is well-characterized, this "noise" can then be subtracted from the TDC output, which ideally would result in a random error that can benefit from oversampling. However, we note that the uncalibrated or residual non-linear quantization error due to mismatch will *not* be corrected with averaging or filtering, since these errors will already have folded in the sampling process to corrupt the bandwidth of interest.

For example, let us consider a high performance Vernier TDC running at 50Msps that has been optimized at the system level to detect small input signals by modulating  $T_{in}$  with a psuedo-random noise source. We can assume that  $T_q$  has been improved by a factor of 4 from the raw gate-delay of 20ps to reach 5ps resolution. Further, a run-time calibration circuit has been designed that allows for compensation of the psuedo-random input sequence and delay element mismatch. Through

this calibration, the effect of mismatch has been reduced from a delay error standard deviation of 10% to an absolute error standard deviation of only 1%, an improvement of over 20dB. The overall rms TDC quantization error for a fixed 50kHz analog bandwidth (typical bandwidth for a  $\Sigma\Delta$  PLL) can then be estimated by the rms sum of quantization noise and mismatch error as

$$T_{error_{rms}} = \sqrt{\frac{T_q^2(2F_b)}{12F_s} + (T_{mm-rms})^2}$$

(2.6)

$$= \sqrt{\frac{(5 \times 10^{-12})^2 (1 \times 10^5)}{12(50 \times 10^6)} + (200 \times 10^{-15})^2}$$

(2.7)

$$= 210fs \tag{2.8}$$

While this result is relatively impressive, it is important to notice two aspects of this example that may be cause for some concern. First, while the rms error due to mismatch without oversampling is negligable, it becomes a dominant source of error once oversampling is leveraged. Since the level of mismatch is only expected to get worse in future CMOS processes, we can now see that this poses a bottleneck for improving the performance of deterministic TDC in the future. The second issue in this example is the level of complexity that was required to achieve the result, both at the component and system levels. As we will soon see, a much simpler TDC implementation in the form of an oscillator has the benefit of inherently scrambled quantization and mismatch error, which makes it well-suited for oversampling applications.

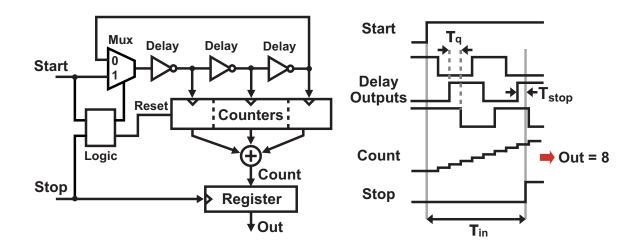

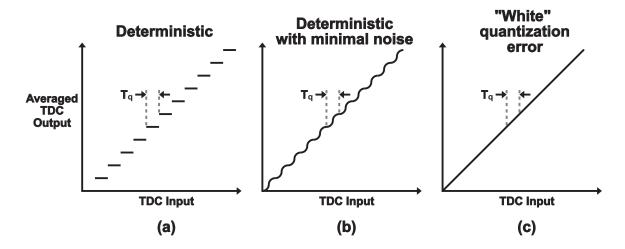

### 2.5 Oscillator-based TDC

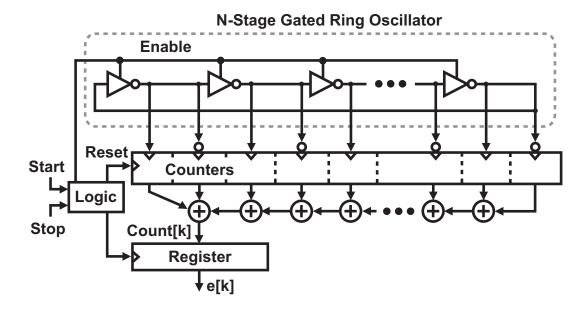

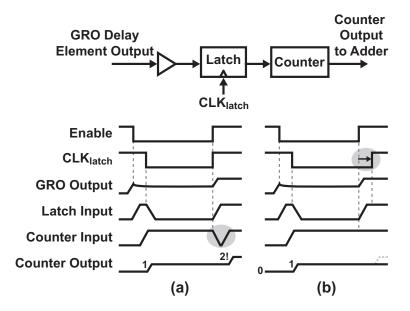

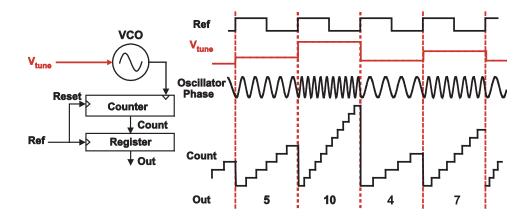

Figure 2-10 illustrates the classical ring oscillator-based TDC composed of a ring of delay elements [46,59], which shares a number of characteristics with the cyclic TDC from Figure 2-4. First, we note that for both topologies the oscillator transitions are counted during the input time window  $T_{in}$ , here designated by the *Enable* signal. Next, all counter outputs are summed together and stored as the TDC output before being reset (during *Enable* low) to prepare for the next measurement. Finally, due

Figure 2-10 Classical oscillator-based TDC

to the logarithmic scaling of the counter range, the oscillator-based TDC also has the attribute of a large dynamic range with reasonable silicon area.

A key difference between the two architectures, however, is found when examining the overall quantization error for the oscillator-based TDC. We find that counting the transitions of a free-running oscillator results in error equivalent to the fundamental expression given earlier by Equation 2.1 and repeated here for convenience,  $T_{error}[k] = T_{stop}[k] - T_{start}[k]$ . Compared with the delay-chain or cyclic TDC error from Equation 2.4, we now include both  $T_{start}$  and  $T_{stop}$ , which indicates that each measurement of the oscillator-based TDC will have an additional error contribution from  $T_{start}$ . For our purposes, we can assume that the oscillator phase at the beginning of each sample is random, and subsequently  $T_{start}$  is also random having uniform density on the interval  $[0, T_q]$ . By way of contrast, the cyclic TDC "phase" is effectively set to 0 at the beginning of each measurement.

To have benefit from oversampling, we thankfully do not require the overall TDC error  $T_{error}$  to also be a random variable with uniform density, as in fact this criteria is quite difficult to satisfy for small inputs. Rather, we require  $T_{error}$  to be a white random variable with flat power spectral density (PSD) across all frequencies and for all inputs, including zero frequency. In addition, we require  $T_{error}$  to be uncorrelated

with  $T_{in}$ . Discussion of the special cases, for example where  $T_{in}$  is exactly equal to an integer multiple of  $T_q$  (i.e.  $T_{error} = 0 \,\forall \, T_{in} = kT_q$ ), will be postponed until later, using the justification for now that this special case ideally occurs with zero probability and can therefore be ignored.

Due to the random properties of  $T_{start}$ , the oscillator-based TDC satisfies the above criteria for  $T_{error}$ . We can expect that the small penalty of larger error for the inclusion of  $T_{start}$  can be easily offset by the resolution improvement by oversampling. Interestingly, the oversampling benefit in the oscillator-based TDC is not constrained to simply improving the quantization error, but also extends to improving errors from mismatch as well.

To further explain how mismatch is also improved by oversampling, we first consider an input  $T_{in}$  that is less than an oscillator period. As mentioned earlier, the oscillator starting phase is random with uniform density, which implies that the delay elements that transition during the Enable window are chosen with a white random process that is independent of the input. Therefore, input intervals that are a fraction of the oscillation period will have mismatch error with flat power spectral density.

Next, we can consider intervals of  $T_{in}$  that are longer than an oscillation period. In this case,  $T_{in}$  can be seen as an interval composed of two parts: an integer number of periods, which does not contribute mismatch error, and the residual fraction of a period that does have mismatch contribution. The argument from the first case can again be used on the residual part of the input with length of less than a period. As a result, we can conclude that for inputs of any length, mismatch error is reduced through oversampling and has no contribution towards integral non-linearity for the oscillator-based TDC.

At this point another example is helpful to quantitatively compare a simple oscillator-based TDC with raw resolution of a gate-delay resolution with the subgate-delay approaches discussed earlier. For this example, let us consider the same sample rate of 50Msps, analog bandwidth of 50kHz, gate-delay of 20ps, and mismatch of 10%. Since we will rely on oversampling to reduce mismatch, we can also assume that there is no calibration. With these parameters set, the overall rms TDC

quantization error is found to be

$$T_{error_{rms}} = \sqrt{\frac{2F_b}{F_s} \left(\frac{2(T_q^2)}{12} + 2(T_{mm-rms})^2\right)}$$

(2.9)

$$= \sqrt{\frac{1 \times 10^5}{50 \times 10^6} \left(\frac{2(20 \times 10^{-12})^2}{12} + 2(2 \times 10^{-12})^2\right)}$$

(2.10)

$$= 367 fs.$$

(2.11)

By comparing the two examples so far, while the simple oscillator TDC achieves resolution performance that is on the same order of the Vernier TDC, the result is achieved with *much simpler* implementation and without input dithering *or* calibration. This demonstrates the benefits of oversampling, not only for improving raw resolution, but also for mitigating the effect of mismatch. The error for the oscillator TDC has raw delay and mismatch components that decrease *together* with oversampling, while the Vernier error has a floor set by the ability to calibrate the mismatch error.

Although the oversampling with the oscillator-based TDC does offer improved resolution, it comes at a fairly expensive penalty in terms of bandwidth and power. In terms of bandwidth, to effectively decrease  $T_q$  by a factor of 2, the oversampling rate would need to be increased by a factor of 4 times the rate. Equivalently, a doubling of the sample rate results in decreasing the quantization error by 3dB, which is a small though helpful improvement. When it comes to power efficiency, in many applications the input signal  $T_{in}$  is quite small compared to the measurement period,  $T_s$ , yet the ring oscillator continues to run freely regardless of the measurement state. This results in wasted power that could otherwise be spent on improving the raw delay resolution of the oscillator.

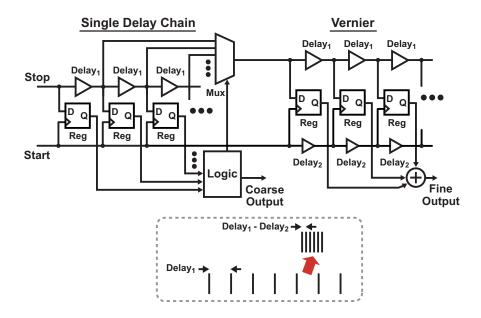

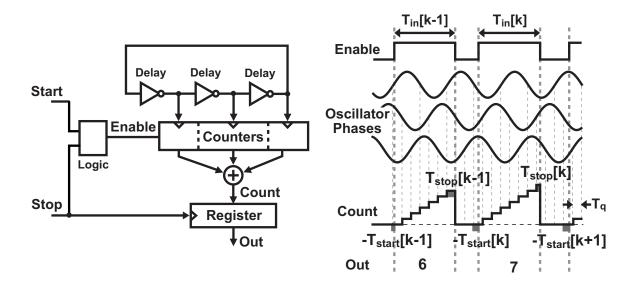

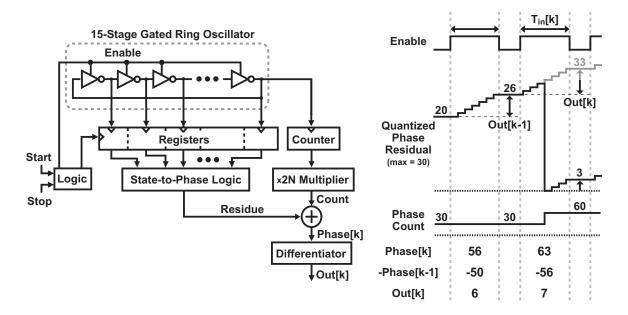

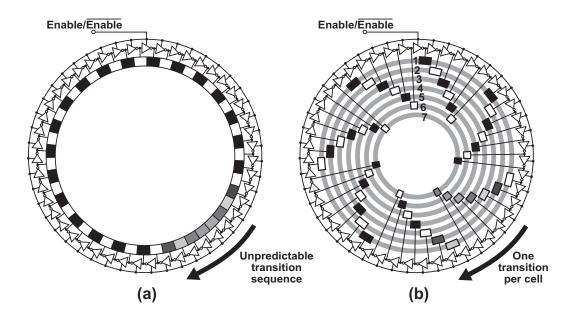

## 2.6 Gated ring oscillator TDC

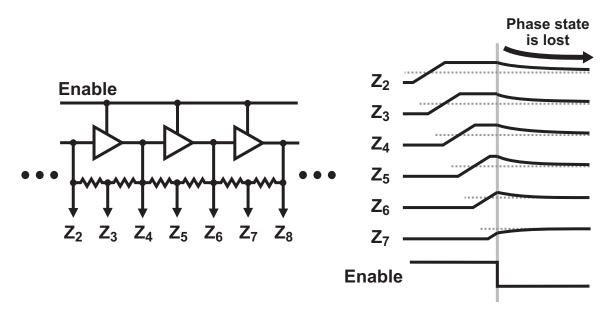

Figure 2-11 illustrates the concept of a gated ring oscillator (GRO) TDC [21, 25], which is again similar to the previous cyclic and oscillator TDC in that it measures

Figure 2-11 Concept of the gated ring oscillator TDC

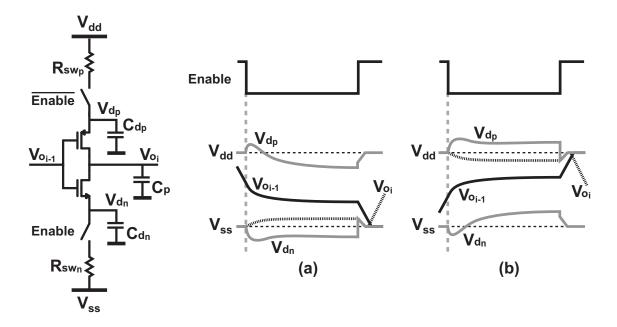

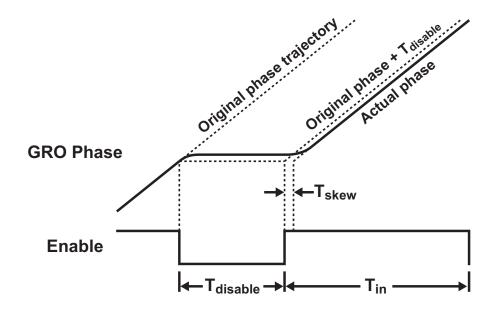

the number of delay element transitions during a measurement interval. Also similar is the ability of the GRO-TDC to achieve large range with a small number of delay elements. However, the key innovation in the gated ring oscillator is that instead of enabling the *counters* during the measurement window, the *ring oscillator* itself is gated with the *Enable* signal, with the state of the oscillator preserved in between measurements.

By preserving the oscillator state at the end of the measurement interval  $T_{in}[k-1]$ , the quantization error  $T_{stop}[k-1]$  from that measurement is also preserved. In fact, when the following measurement of  $T_{in}[k]$  is initiated, the previous quantization error is carried over as  $T_{start}[k] = T_{stop}[k-1]$ . This results in first-order noise shaping of the quantization error in the frequency domain, as evidenced by the first-order difference operation on  $T_{stop}$  since the measurement error is given by

$$T_{error}[k] = T_{stop}[k] - T_{stop}[k-1].$$

(2.12)

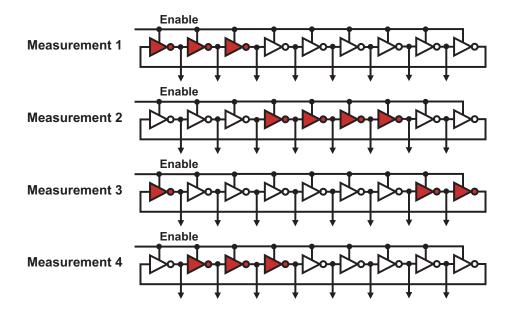

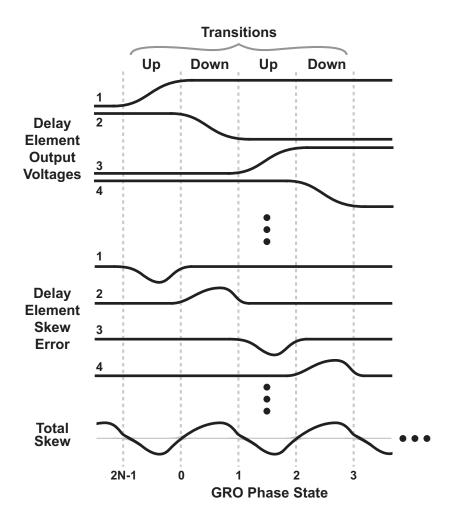

A subtle aspect to the GRO-TDC is that, along with the quantization noise, the delay element mismatch is also first-order shaped. To see this more clearly, let us examine the sequencing of delay elements for successive TDC conversions, as

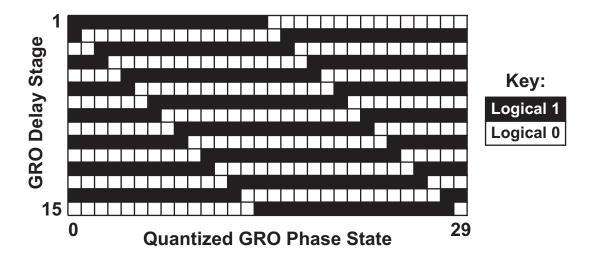

Figure 2-12 Barrel-shifting of GRO delay elements to achieve first-order shaping of mismatch error

shown in Figure 2-12. What is clearly evident in this figure is that the selection of delay elements for a given input is equivalent to the well-known barrel-shift algorithm for dynamic element matching. Similar to the transfer of quantization error, the mismatch errors for one sample are also passed along to and subtracted from the following sample. Therefore, we can expect that in the case of oversampling, the GRO-TDC architecture ideally achieves high resolution without the need for calibration, even in the presence of large mismatch.

Now comparing the GRO-TDC to the oscillator-based TDC for a single-shot measurement, the GRO-TDC will have the same additional quantization error penalty found in Equation 2.1. However, when considering again the benefits from oversampling, the GRO-TDC quantization error will ideally decrease by 9dB for a doubling of the sample rate, which is a significant improvement compared to the 3dB possible for the oscillator TDC. This relationship can be clearly seen in the expression for rms TDC quantization error

$$T_{error_{rms}} = \sqrt{\left(\frac{T_q}{2}\right)^2 \frac{1}{9\pi} \left(\frac{2\pi F_b}{F_s}\right)^3} \tag{2.13}$$

An example GRO-TDC using the same parameters as the previous oscillator example will then ideally have rms TDC quantization error of only

$$T_{error_{rms}} = \sqrt{\left(\frac{20 \times 10^{-12}}{2}\right)^2 \frac{1}{9\pi} \left(\frac{2\pi 5 \times 10^4}{50 \times 10^6}\right)^3}$$

(2.14)

$$= 0.9fs!$$

(2.15)

While this ideal performance level is far below typical thermal and 1/f noise levels for digital CMOS, even the *potential* to achieve TDC resolution that is limited by physical processes in a simple architecture is very compelling. The combination of oversampling with first-order quantization noise and mismatch shaping is quite powerful and can result in very high resolution conversion. Moreover, as will be seen in the following sections, the GRO-TDC requires only a modest level of complexity that can be implemented with small area and power consumption.

# Chapter 3

# Detailed GRO operation

# 3.1 Simple Gated Ring Oscillator Implementation

While first-order quantization noise shaping is very appealing for many applications, it is yet unclear that preserving a ring oscillator state through the stop and start operation is possible, and even more unclear is whether a simple circuit topology can yield useful and practical results. Because the noise shaping we desire depends on the accurate transfer of quantization error from one measurement to the next (i.e.  $T_{start}[k] = T_{stop}[k-1]$ ), it is important to consider how well this can be accomplished with simple circuitry, and also how imprecise error transfer will affect noise-shaping. Towards this end, we now consider a simple circuit topology to illustrate the key design challenges of the gated ring oscillator.

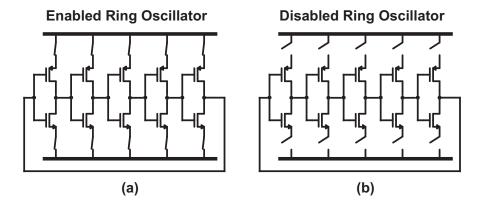

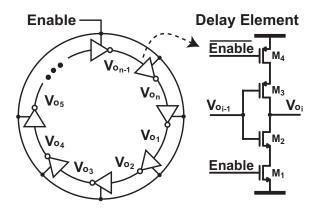

### 3.1.1 GRO with inverter delay stages

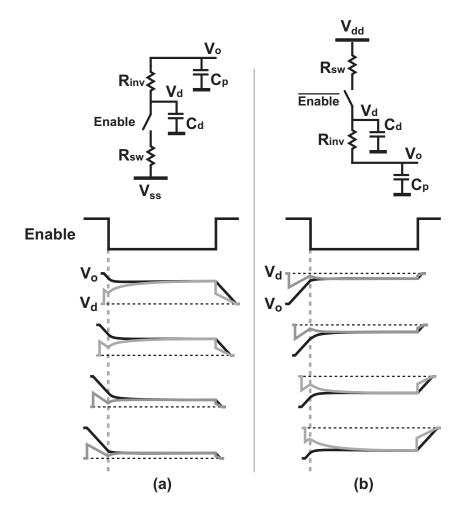

Figure 3-1 illustrates one potential implementation for gating a ring oscillator by using switches [21]. Starting from a classical inverter-based ring oscillator with an odd number of stages, these switches are added in series to the positive and negative power supply connections for each inverter, and all switches share a common state. When the switches are closed, oscillation is enabled and the ring of inverters behaves identically to a classical ring oscillator (Figure 3-1(a)). Conversely, when the switches

Figure 3-1 Conceptual implementation of gating a ring oscillator

Figure 3-2 Transistor-level schematic of a simple GRO

are open, the inverter delay element is unable to charge or discharge the parasitic output capacitance, and as a result oscillation is suspended (Figure 3-1(b)). The oscillator phase at the end of the enabled state is then held during the disabled state with the charge stored on the parasitic capacitance of the delay elements.